## Sumin Choi

List of Publications by Year in descending order

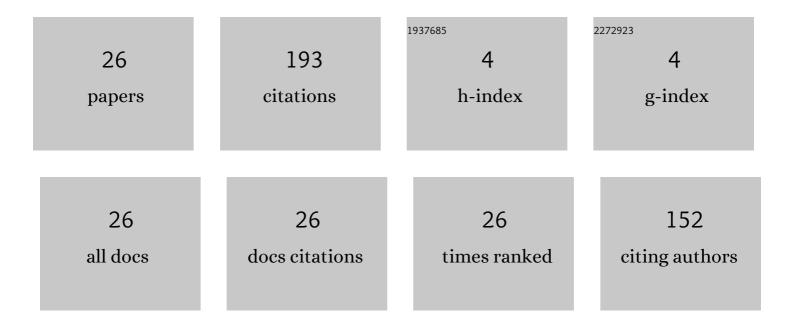

Source: https://exaly.com/author-pdf/7824304/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                                                                                   | IF  | CITATIONS |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | Signal Integrity Design and Analysis of Silicon Interposer for GPU-Memory Channels in<br>High-Bandwidth Memory Interface. IEEE Transactions on Components, Packaging and Manufacturing<br>Technology, 2018, 8, 1658-1671. | 2.5 | 40        |

| 2  | Design and Analysis of Power Distribution Network (PDN) for High Bandwidth Memory (HBM)<br>Interposer in 2.5D Terabyte/s Bandwidth Graphics Module. , 2016, , .                                                           |     | 24        |

| 3  | Design optimization of high bandwidth memory (HBM) interposer considering signal integrity. , 2015, , .                                                                                                                   |     | 21        |

| 4  | Modeling and Analysis of TSV Noise Coupling Effects on RF LC-VCO and Shielding Structures in 3D IC.<br>IEEE Transactions on Electromagnetic Compatibility, 2018, 60, 1939-1947.                                           | 2.2 | 14        |

| 5  | Power distribution network (PDN) design and analysis of a single and double-sided high bandwidth<br>memory (HBM) interposer for 2.5D Terabtye/s bandwidth system. , 2016, , .                                             |     | 13        |

| 6  | A Novel Stochastic Model-Based Eye-Diagram Estimation Method for 8B/10B and TMDS-Encoded<br>High-Speed Channels. IEEE Transactions on Electromagnetic Compatibility, 2018, 60, 1510-1519.                                 | 2.2 | 13        |

| 7  | Electrical performance of high bandwidth memory (HBM) interposer channel in terabyte/s bandwidth<br>graphics module. , 2015, , .                                                                                          |     | 9         |

| 8  | Signal Integrity Analysis of Silicon/Glass/Organic Interposers for 2.5D/3D Interconnects. , 2017, , .                                                                                                                     |     | 9         |

| 9  | A Novel Eye-Diagram Estimation Method for Pulse Amplitude Modulation With <i>N</i> -Level (PAM-N)<br>on Stacked Through-Silicon Vias. IEEE Transactions on Electromagnetic Compatibility, 2019, 61,<br>1198-1206.         | 2.2 | 8         |

| 10 | Crosstalk included eye diagram estimation of high-speed and wide I/O interposer channel for 2.5D / 3D IC. , 2014, , .                                                                                                     |     | 5         |

| 11 | Eye-diagram estimation and analysis of High-Bandwidth Memory (HBM) interposer channel with crosstalk reduction schemes on 2.5D and 3D IC. , 2016, , .                                                                     |     | 5         |

| 12 | Shielding structures for through silicon via (TSV) to active circuit noise coupling in 3D IC. , 2015, , .                                                                                                                 |     | 4         |

| 13 | Signal and power integrity (SI/PI) analysis of heterogeneous integration using embedded multi-die<br>interconnect bridge (EMIB) technology for high bandwidth memory (HBM). , 2017, , .                                   |     | 4         |

| 14 | Eye-Diagram Estimation Methods for Voltage-and Probability-Dependent PAM-4 Signal on Stacked<br>Through-Silicon Vias (TSVs). , 2017, , .                                                                                  |     | 4         |

| 15 | Design and Analysis of a 10 Gbps USB 3.2 Gen 2 Type-C Connector for TV Set-Top Box. , 2019, , .                                                                                                                           |     | 4         |

| 16 | Signal Integrity of Bump-Less High-Speed through Silicon Via Channel for Terabyte/s Bandwidth 2.5D IC.<br>, 2016, , .                                                                                                     |     | 3         |

| 17 | Modeling and analysis of high-speed through silicon via (TSV) channel and defects. , 2016, , .                                                                                                                            |     | 3         |

| 18 | Crosstalk-included eye-diagram estimation for high-speed silicon, organic, and glass interposer                                                                                                                           |     | 2         |

channels on 2.5D/3D IC. , 2015, , .

**SUMIN CHOI**

| #  | Article                                                                                                                                                | IF | CITATIONS |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------|

| 19 | Eye-diagram estimation using equivalent circuit model of coupled microstrip channel on high-speed and wide I/O Channel for 2.5D and 3D IC. , 2016, , . |    | 2         |

| 20 | Eye-diagram estimation with stochastic model for 8B/10B encoded high-speed channel. , 2018, , .                                                        |    | 2         |

| 21 | Statistical eye-diagram estimation method for high-speed channel with N-tap decision feedback equalizer (DFE). , 2018, , .                             |    | 2         |

| 22 | Design of an on-interposer passive equalizer embedded on a ground plane for 30Gbps serial data transmission. , 2015, , .                               |    | 1         |

| 23 | Design of an On-Interposer Passive Equalizer for High Bandwidth Memory (HBM) with 30Gbps Data<br>Transmission. , 2016, , .                             |    | 1         |

| 24 | Electrical characterization of bump-less high speed channel on silicon, organic and glass interposer. , 2014, , .                                      |    | 0         |

| 25 | Signal integrity design of bump-less interconnection for high-speed signaling in 2.5D and 3D IC. , 2015, ,                                             |    | 0         |

| 26 | Estimation and analysis of crosstalk effects in high-bandwidth memory channel. , 2018, , .                                                             |    | 0         |