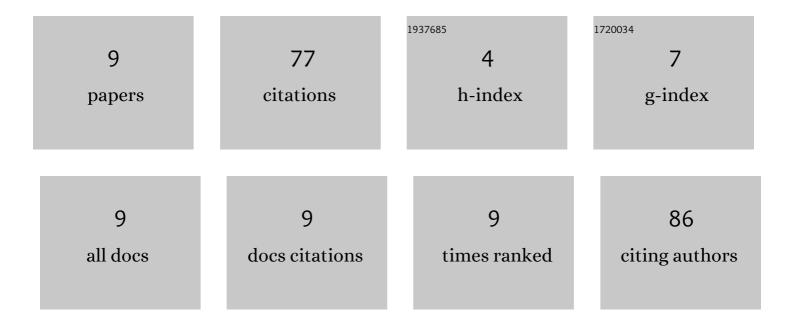

## Tram Thi Bao Nguyen

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/7600855/publications.pdf Version: 2024-02-01

| # | Article                                                                                                                                                                               | IF  | CITATIONS |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1 | Low-Complexity Multi-Size Circular-Shift Network for 5G New Radio LDPC Decoders. Sensors, 2022, 22, 1792.                                                                             | 3.8 | 2         |

| 2 | An Analysis of Hardware Design of MLWE-Based Public-Key Encryption and Key-Establishment<br>Algorithms. Electronics (Switzerland), 2022, 11, 891.                                     | 3.1 | 2         |

| 3 | Low-Complexity High-Throughput QC-LDPC Decoder for 5G New Radio Wireless Communication.<br>Electronics (Switzerland), 2021, 10, 516.                                                  | 3.1 | 16        |

| 4 | High Efficiency Ring-LWE Cryptoprocessor Using Shared Arithmetic Components. Electronics (Switzerland), 2020, 9, 1075.                                                                | 3.1 | 0         |

| 5 | Efficient QC-LDPC Encoder for 5G New Radio. Electronics (Switzerland), 2019, 8, 668.                                                                                                  | 3.1 | 39        |

| 6 | Low-complexity multi-mode multi-way split-row layered LDPC decoder for gigabit wireless communications. The Integration VLSI Journal, 2019, 65, 189-200.                              | 2.1 | 8         |

| 7 | Efficient Four-way Row-splitting Layered QC-LDPC Decoder Architecture. , 2018, , .                                                                                                    |     | 1         |

| 8 | An Area-efficient Half-row Pipelined Layered LDPC Decoder Architecture. Journal of Semiconductor<br>Technology and Science, 2017, 17, 845-853.                                        | 0.4 | 4         |

| 9 | High-throughput Low-complexity Mixed-radix FFT Processor using a Dual-path Shared Complex<br>Constant Multiplier. Journal of Semiconductor Technology and Science, 2017, 17, 101-109. | 0.4 | 5         |