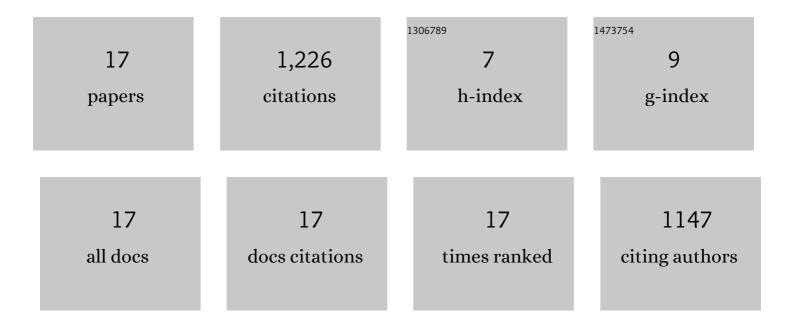

## Ning Qiao

## List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/7307141/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                                                                          | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | Ultra-Low-Power FDSOI Neural Circuits for Extreme-Edge Neuromorphic Intelligence. IEEE<br>Transactions on Circuits and Systems I: Regular Papers, 2021, 68, 45-56.                                               | 3.5 | 42        |

| 2  | Robust Learning and Recognition of Visual Patterns in Neuromorphic Electronic Agents. , 2019, , .                                                                                                                |     | 3         |

| 3  | ECG-based Heartbeat Classification in Neuromorphic Hardware. , 2019, , .                                                                                                                                         |     | 34        |

| 4  | Neural State Machines for Robust Learning and Control of Neuromorphic Agents. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2019, 9, 679-689.                                            | 2.7 | 11        |

| 5  | A Scalable Multicore Architecture With Heterogeneous Memory Structures for Dynamic<br>Neuromorphic Asynchronous Processors (DYNAPs). IEEE Transactions on Biomedical Circuits and<br>Systems, 2018, 12, 106-122. | 2.7 | 377       |

| 6  | A Clock-Less Ultra-Low Power Bit-Serial LVDS Link for Address-Event Multi-chip Systems. , 2018, , .                                                                                                              |     | 0         |

| 7  | Large-Scale Neuromorphic Spiking Array Processors: A Quest to Mimic the Brain. Frontiers in<br>Neuroscience, 2018, 12, 891.                                                                                      | 1.4 | 177       |

| 8  | A bi-directional Address-Event transceiver block for low-latency inter-chip communication in neuromorphic systems. , 2018, , .                                                                                   |     | 1         |

| 9  | Organizing Sequential Memory in a Neuromorphic Device Using Dynamic Neural Fields. Frontiers in Neuroscience, 2018, 12, 717.                                                                                     | 1.4 | 8         |

| 10 | An Ultralow Leakage Synaptic Scaling Homeostatic Plasticity Circuit With Configurable Time Scales up to 100 ks. IEEE Transactions on Biomedical Circuits and Systems, 2017, 11, 1271-1277.                       | 2.7 | 24        |

| 11 | Automatic gain control of ultra-low leakage synaptic scaling homeostatic plasticity circuits. , 2016, , .                                                                                                        |     | 3         |

| 12 | An auto-scaling wide dynamic range current to frequency converter for real-time monitoring of signals in neuromorphic systems. , 2016, , .                                                                       |     | 3         |

| 13 | Scaling mixed-signal neuromorphic processors to 28 nm FD-SOI technologies. , 2016, , .                                                                                                                           |     | 38        |

| 14 | Wide dynamic range weights and biologically realistic synaptic dynamics for spike-based learning circuits. , 2016, , .                                                                                           |     | 4         |

| 15 | A reconfigurable on-line learning spiking neuromorphic processor comprising 256 neurons and 128K synapses. Frontiers in Neuroscience, 2015, 9, 141.                                                              | 1.4 | 496       |

| 16 | A 10-bit 50-MS/s reference-free low power SAR ADC in 0.18-μm SOI CMOS technology. Journal of Semiconductors, 2012, 33, 095005.                                                                                   | 2.0 | 3         |

| 17 | A 14-bit wide temperature range differential SAR ADC with an on-chip multi-segment BGR. Journal of Semiconductors, 2011, 32, 085003.                                                                             | 2.0 | 2         |