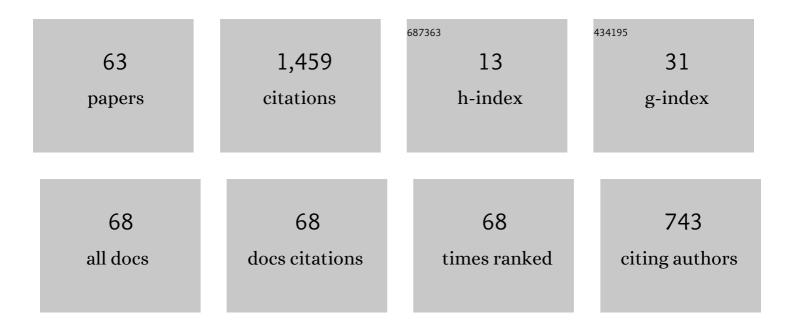

## **Chrysostomos Nicopoulos**

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/664786/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                                                                          | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | Design and Management of 3D Chip Multiprocessors Using Network-in-Memory. Computer<br>Architecture News, 2006, 34, 130-141.                                                                                      | 2.5 | 244       |

| 2  | ViChaR: A Dynamic Virtual Channel Regulator for Network-on-Chip Routers. Microarchitecture<br>(MICRO), Proceedings of the Annual International Symposium on, 2006, , .                                           | 0.0 | 172       |

| 3  | A novel dimensionally-decomposed router for on-chip communication in 3D architectures. , 2007, , .                                                                                                               |     | 168       |

| 4  | A Gracefully Degrading and Energy-Efficient Modular Router Architecture for On-Chip Networks.<br>Computer Architecture News, 2006, 34, 4-15.                                                                     | 2.5 | 131       |

| 5  | NoCAlert: An On-Line and Real-Time Fault Detection Mechanism for Network-on-Chip Architectures. ,<br>2012, , .                                                                                                   |     | 71        |

| 6  | Performance and power optimization through data compression in Network-on-Chip architectures.<br>High Performance Computer Architecture (HPCA), Proceedings of the IEEE International Symposium<br>on, 2008, , . | 0.0 | 56        |

| 7  | On the Effects of Process Variation in Network-on-Chip Architectures. IEEE Transactions on Dependable and Secure Computing, 2010, 7, 240-254.                                                                    | 5.4 | 50        |

| 8  | An energy- and performance-aware DRAM cache architecture for hybrid DRAM/PCM main memory systems. , 2011, , .                                                                                                    |     | 41        |

| 9  | Optimizing Data-Center TCO with Scale-Out Processors. IEEE Micro, 2012, 32, 52-63.                                                                                                                               | 1.8 | 32        |

| 10 | Do we need wide flits in Networks-on-Chip?. , 2013, , .                                                                                                                                                          |     | 30        |

| 11 | Variation-Aware Task and Communication Mapping for MPSoC Architecture. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30, 295-307.                                         | 2.7 | 27        |

| 12 | ShortPath: A Network-on-Chip Router with Fine-Grained Pipeline Bypassing. IEEE Transactions on Computers, 2016, 65, 3136-3147.                                                                                   | 3.4 | 25        |

| 13 | A Compression-Based Hybrid MLC/SLC Management Technique for Phase-Change Memory Systems. , 2012, , ,                                                                                                             |     | 24        |

| 14 | A Dynamically Adjusting Gracefully Degrading Link-Level Fault-Tolerant Mechanism for NoCs. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2012, 31, 1235-1248.                | 2.7 | 23        |

| 15 | Designing Hybrid DRAM/PCM Main Memory Systems Utilizing Dual-Phase Compression. ACM Transactions on Design Automation of Electronic Systems, 2014, 20, 1-31.                                                     | 2.6 | 21        |

| 16 | Design of a Dynamic Priority-Based Fast Path Architecture for On-Chip Interconnects. , 2007, , .                                                                                                                 |     | 19        |

| 17 | Virtualizing Virtual Channels for Increased Network-on-Chip Robustness and Upgradeability. , 2012, , .                                                                                                           |     | 19        |

| 18 | ElastiStore: Flexible Elastic Buffering for Virtual-Channel-Based Networks on Chip. IEEE Transactions<br>on Very Large Scale Integration (VLSI) Systems, 2015, 23, 3015-3028.                                    | 3.1 | 19        |

| #  | Article                                                                                                                                                                                               | IF  | CITATIONS |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | Thermal characterization of cloud workloads on a power-efficient server-on-chip. , 2012, , .                                                                                                          |     | 18        |

| 20 | ECM: Effective Capacity Maximizer for high-performance compressed caching. , 2013, , .                                                                                                                |     | 16        |

| 21 | A Distributed Multi-Point Network Interface for Low-Latency, Deadlock-Free On-Chip Interconnects. ,<br>2006, , .                                                                                      |     | 14        |

| 22 | A dual-phase compression mechanism for hybrid DRAM/PCM main memory architectures. , 2012, , .                                                                                                         |     | 14        |

| 23 | Networks-on-Chip With Double-Data-Rate Links. IEEE Transactions on Circuits and Systems I: Regular<br>Papers, 2017, 64, 3103-3114.                                                                    | 5.4 | 14        |

| 24 | Dynamic faultâ€ŧolerant routing algorithm for networksâ€onâ€chip based on localised detouring paths. IET<br>Computers and Digital Techniques, 2013, 7, 93-103.                                        | 1.2 | 13        |

| 25 | A Low-Power Network-on-Chip Architecture for Tile-based Chip Multi-Processors. , 2016, , .                                                                                                            |     | 13        |

| 26 | PhaseNoC: Versatile Network Traffic Isolation Through TDM-Scheduled Virtual Channels. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2016, 35, 844-857.            | 2.7 | 13        |

| 27 | IsoNet: Hardware-Based Job Queue Management for Many-Core Architectures. IEEE Transactions on<br>Very Large Scale Integration (VLSI) Systems, 2013, 21, 1080-1093.                                    | 3.1 | 12        |

| 28 | A fine-grained link-level fault-tolerant mechanism for networks-on-chip. , 2010, , .                                                                                                                  |     | 10        |

| 29 | An Online and Real-Time Fault Detection and Localization Mechanism for Network-on-Chip<br>Architectures. Transactions on Architecture and Code Optimization, 2016, 13, 1-26.                          | 2.0 | 10        |

| 30 | A Dual-Clock Multiple-Queue Shared Buffer. IEEE Transactions on Computers, 2017, 66, 1809-1815.                                                                                                       | 3.4 | 10        |

| 31 | Field Programmable Compressor Trees. ACM Transactions on Reconfigurable Technology and Systems, 2009, 2, 1-36.                                                                                        | 2.5 | 9         |

| 32 | Size-Aware Cache Management for Compressed Cache Architectures. IEEE Transactions on Computers, 2015, 64, 2337-2352.                                                                                  | 3.4 | 9         |

| 33 | Timing-Driven Placement Optimization Facilitated by Timing-Compatibility Flip-Flop Clustering. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2020, 39, 2835-2848. | 2.7 | 9         |

| 34 | The Mesochronous Dual-Clock FIFO Buffer. IEEE Transactions on Very Large Scale Integration (VLSI)<br>Systems, 2020, 28, 302-306.                                                                      | 3.1 | 9         |

| 35 | A Hardware-assisted Heartbeat Mechanism for Fault Identification in Large-scale IoT Systems. IEEE Transactions on Dependable and Secure Computing, 2020, , 1-1.                                       | 5.4 | 9         |

| 36 | Variation-Aware Low-Power Buffer Design. Conference Record of the Asilomar Conference on<br>Signals, Systems and Computers, 2007, , .                                                                 | 0.0 | 6         |

| #  | Article                                                                                                                                                                                                   | IF  | CITATIONS |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 37 | A highly robust distributed fault-tolerant routing algorithm for NoCs with localized rerouting. ,<br>2012, , .                                                                                            |     | 6         |

| 38 | TornadoNoC. Transactions on Architecture and Code Optimization, 2013, 10, 1-30.                                                                                                                           | 2.0 | 6         |

| 39 | Low-Cost Online Convolution Checksum Checker. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2022, 30, 201-212.                                                                        | 3.1 | 6         |

| 40 | Multi-Armed Bandits for Autonomous Timing-driven Design Optimization. , 2019, , .                                                                                                                         |     | 5         |

| 41 | Autonomous Application of Netlist Transformations Inside Lagrangian Relaxation-Based Optimization.<br>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2021, 40, 1672-1686. | 2.7 | 5         |

| 42 | Design of a Dynamic Priority-Based Fast Path Architecture for On-Chip Interconnects. , 2007, , .                                                                                                          |     | 5         |

| 43 | Large-Scale Semantic Concept Detection on Manycore Platforms for Multimedia Mining. , 2011, , .                                                                                                           |     | 4         |

| 44 | Hardware-Based Online Self-Diagnosis for Faulty Device Identification in Large-Scale IoT Systems. ,<br>2018, , .                                                                                          |     | 4         |

| 45 | Automatic Generation of Peak-Power Traffic for Networks-on-Chip. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2019, 38, 96-108.                                         | 2.7 | 4         |

| 46 | Analysis and solutions to issue queue process variation. , 2008, , .                                                                                                                                      |     | 3         |

| 47 | Hardware-Based Job Queue Management for Manycore Architectures and OpenMP Environments. , 2011, , , $\cdot$                                                                                               |     | 3         |

| 48 | Practical Verifiable Computation by Using a Hardware-Based Correct Execution Environment. IEEE<br>Access, 2020, 8, 216689-216706.                                                                         | 4.2 | 3         |

| 49 | Design Optimization by Fine-grained Interleaving of Local Netlist Transformations in Lagrangian Relaxation. , 2020, , .                                                                                   |     | 3         |

| 50 | Design space exploration for field programmable compressor trees. , 2008, , .                                                                                                                             |     | 2         |

| 51 | A High-Performance and Energy-Efficient Virtually Tagged Stack Cache Architecture for Multi-core<br>Environments. , 2011, , .                                                                             |     | 2         |

| 52 | A programmable processing array architecture supporting dynamic task scheduling and module-level prefetching. , 2012, , .                                                                                 |     | 2         |

| 53 | Sharded Router: A novel on-chip router architecture employing bandwidth sharding and stealing.<br>Parallel Computing, 2013, 39, 372-388.                                                                  | 2.1 | 2         |

| 54 | Centaur: a hybrid network-on-chip architecture utilizing micro-network fusion. Design Automation<br>for Embedded Systems, 2014, 18, 121-139.                                                              | 1.0 | 2         |

| #  | Article                                                                                                                                  | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 55 | HARPA: Solutions for dependable performance under physically induced performance variability. , 2015, , .                                |     | 2         |

| 56 | Powermax: an automated methodology for generating peak-power traffic in networks-on-chip. , 2016, ,                                      |     | 2         |

| 57 | Timing-resilient Network-on-Chip architectures. , 2015, , .                                                                              |     | 1         |

| 58 | RapidLink: A network-on-chip architecture with double-data-rate links. , 2016, , .                                                       |     | 1         |

| 59 | Toward Multi-Layer Holistic Evaluation of System Designs. IEEE Computer Architecture Letters, 2016, 15, 58-61.                           | 1.5 | 1         |

| 60 | Low-power dual-edge-triggered synchronous latency-insensitive systems. , 2018, , .                                                       |     | 1         |

| 61 | Subtleties of Run-Time Virtual Address Stacks. IEEE Computer Architecture Letters, 2015, 14, 152-155.                                    | 1.5 | 0         |

| 62 | Dynamic Adjustment of Test-Sequence Duration for Increasing the Functional Coverage. , 2019, , .                                         |     | 0         |

| 63 | Hardware-Assisted Intrusion Detection by Preserving Reference Information Integrity. Lecture Notes in Computer Science, 2013, , 291-300. | 1.3 | 0         |