List of Publications by Year in descending order

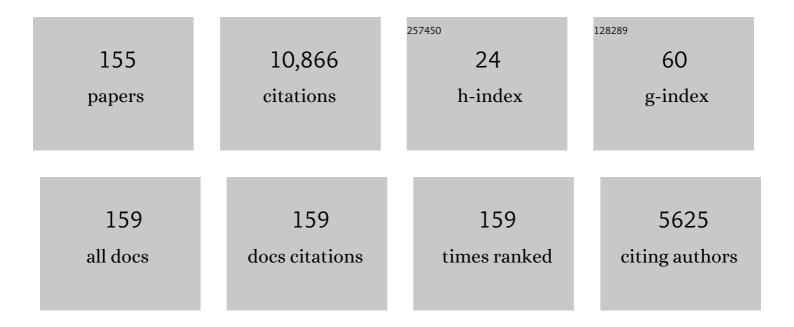

Source: https://exaly.com/author-pdf/6267704/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                              | IF   | CITATIONS |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|

| 1  | Rodinia: A benchmark suite for heterogeneous computing. , 2009, , .                                                                                                  |      | 2,150     |

| 2  | Scalable Parallel Programming with CUDA. Queue, 2008, 6, 40-53.                                                                                                      | 1.1  | 1,344     |

| 3  | HotSpot: a compact thermal modeling methodology for early-stage VLSI design. IEEE Transactions on<br>Very Large Scale Integration (VLSI) Systems, 2006, 14, 501-513. | 3.1  | 860       |

| 4  | Temperature-aware microarchitecture. , 2003, , .                                                                                                                     |      | 695       |

| 5  | Temperature-aware microarchitecture. Transactions on Architecture and Code Optimization, 2004, 1, 94-125.                                                            | 2.0  | 640       |

| 6  | A performance study of general-purpose applications on graphics processors using CUDA. Journal of<br>Parallel and Distributed Computing, 2008, 68, 1370-1380.        | 4.1  | 496       |

| 7  | Temperature-aware microarchitecture. Computer Architecture News, 2003, 31, 2-13.                                                                                     | 2.5  | 275       |

| 8  | Dynamic Voltage Scaling in Multitier Web Servers with End-to-End Delay Control. IEEE Transactions on Computers, 2007, 56, 444-458.                                   | 3.4  | 219       |

| 9  | Accelerating Compute-Intensive Applications with GPUs and FPGAs. , 2008, , .                                                                                         |      | 212       |

| 10 | A characterization of the Rodinia benchmark suite with comparison to contemporary CMP workloads. , 2010, , .                                                         |      | 211       |

| 11 | Compact thermal modeling for temperature-aware design. , 2004, , .                                                                                                   |      | 191       |

| 12 | Accelerating SQL database operations on a GPU with CUDA. , 2010, , .                                                                                                 |      | 181       |

| 13 | Recent thermal management techniques for microprocessors. ACM Computing Surveys, 2012, 44, 1-42.                                                                     | 23.0 | 167       |

| 14 | Dynamic warp subdivision for integrated branch and memory divergence tolerance. , 2010, , .                                                                          |      | 166       |

| 15 | Pannotia: Understanding irregular GPGPU graph applications. , 2013, , .                                                                                              |      | 119       |

| 16 | Performance modeling and automatic ghost zone optimization for iterative stencil loops on GPUs. , 2009, , .                                                          |      | 103       |

| 17 | Scaling with Design Constraints: Predicting the Future of Big Chips. IEEE Micro, 2011, 31, 16-29.                                                                    | 1.8  | 100       |

| 18 | Temperature-aware computer systems: opportunities and challenges. IEEE Micro, 2003, 23, 52-61.                                                                       | 1.8  | 99        |

| #  | Article                                                                                                                                                            | IF  | CITATIONS |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | Accurate, Pre-RTL Temperature-Aware Design Using a Parameterized, Geometric Thermal Model. IEEE<br>Transactions on Computers, 2008, 57, 1277-1288.                 | 3.4 | 92        |

| 20 | Multi-mode energy management for multi-tier server clusters. , 2008, , .                                                                                           |     | 92        |

| 21 | Impact of Process Variations on Multicore Performance Symmetry. , 2007, , .                                                                                        |     | 89        |

| 22 | HotSpot: a dynamic compact thermal model at the processor-architecture level. Microelectronics<br>Journal, 2003, 34, 1153-1165.                                    | 2.0 | 88        |

| 23 | Control-theoretic dynamic frequency and voltage scaling for multimedia workloads. , 2002, , .                                                                      |     | 83        |

| 24 | Dymaxion. , 2011, , .                                                                                                                                              |     | 80        |

| 25 | Many-core design from a thermal perspective. , 2008, , .                                                                                                           |     | 79        |

| 26 | Predictive Temperature-Aware DVFS. IEEE Transactions on Computers, 2010, 59, 127-133.                                                                              | 3.4 | 78        |

| 27 | Branch prediction, instruction-window size, and cache size: performance trade-offs and simulation techniques. IEEE Transactions on Computers, 1999, 48, 1260-1281. | 3.4 | 75        |

| 28 | Binary Interval Search: a scalable algorithm for counting interval intersections. Bioinformatics, 2013, 29, 1-7.                                                   | 4.1 | 58        |

| 29 | Association Rule Mining with the Micron Automata Processor. , 2015, , .                                                                                            |     | 51        |

| 30 | Power-aware computing. Computer, 2003, 36, 35-38.                                                                                                                  | 1.1 | 49        |

| 31 | ANMLzoo: a benchmark suite for exploring bottlenecks in automata processing engines and architectures. , 2016, , .                                                 |     | 48        |

| 32 | Increasing memory miss tolerance for SIMD cores. , 2009, , .                                                                                                       |     | 47        |

| 33 | Accelerating leukocyte tracking using CUDA: A case study in leveraging manycore coprocessors. , 2009, , .                                                          |     | 45        |

| 34 | CLEAR. , 2016, , .                                                                                                                                                 |     | 45        |

| 35 | Real-world design and evaluation of compiler-managed GPU redundant multithreading. , 2014, , .                                                                     |     | 44        |

| 36 | Differentiating the roles of IR measurement and simulation for power and temperature-aware design. ,<br>2009, , .                                                  |     | 42        |

| #  | Article                                                                                                                                                     | IF  | CITATIONS |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 37 | Power-aware branch prediction: characterization and design. IEEE Transactions on Computers, 2004, 53, 168-186.                                              | 3.4 | 39        |

| 38 | Dynamic warp subdivision for integrated branch and memory divergence tolerance. Computer Architecture News, 2010, 38, 235-246.                              | 2.5 | 39        |

| 39 | Interconnect Lifetime Prediction for Reliability-Aware Systems. IEEE Transactions on Very Large Scale<br>Integration (VLSI) Systems, 2007, 15, 159-172.     | 3.1 | 38        |

| 40 | Increasing Utilization in Modern Warehouse-Scale Computers Using Bubble-Up. IEEE Micro, 2012, 32,<br>88-99.                                                 | 1.8 | 38        |

| 41 | A Performance Study for Iterative Stencil Loops on GPUs with Ghost Zone Optimizations.<br>International Journal of Parallel Programming, 2011, 39, 115-142. | 1.5 | 37        |

| 42 | Federation. , 2008, , .                                                                                                                                     |     | 34        |

| 43 | Architecture implications of pads as a scarce resource. , 2014, , .                                                                                         |     | 34        |

| 44 | Implications of the Power Wall: Dim Cores and Reconfigurable Logic. IEEE Micro, 2013, 33, 40-48.                                                            | 1.8 | 33        |

| 45 | Sequential pattern mining with the Micron automata processor. , 2016, , .                                                                                   |     | 32        |

| 46 | Using cycle stacks to understand scaling bottlenecks in multi-threaded workloads. , 2011, , .                                                               |     | 31        |

| 47 | Brill tagging on the Micron Automata Processor. , 2015, , .                                                                                                 |     | 31        |

| 48 | A Hierarchical Thread Scheduler and Register File for Energy-Efficient Throughput Processors. ACM<br>Transactions on Computer Systems, 2012, 30, 1-38.      | 0.8 | 30        |

| 49 | Improved Thermal Management with Reliability Banking. IEEE Micro, 2005, 25, 40-49.                                                                          | 1.8 | 29        |

| 50 | Energy-efficient mechanisms for managing thread context in throughput processors. Computer<br>Architecture News, 2011, 39, 235-246.                         | 2.5 | 29        |

| 51 | Predictive design space exploration using genetically programmed response surfaces. , 2008, , .                                                             |     | 26        |

| 52 | Understanding the energy efficiency of simultaneous multithreading. , 2004, , .                                                                             |     | 25        |

| 53 | Impala: Algorithm/Architecture Co-Design for In-Memory Multi-Stride Pattern Matching. , 2020, , .                                                           |     | 25        |

| 54 | SPEC ACCEL: A Standard Application Suite for Measuring Hardware Accelerator Performance. Lecture<br>Notes in Computer Science, 2015, , 46-67.               | 1.3 | 24        |

| #  | Article                                                                                                                                | IF  | CITATIONS |

|----|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 55 | REAPR: Reconfigurable engine for automata processing. , 2017, , .                                                                      |     | 23        |

| 56 | Searching for Potential gRNA Off-Target Sites for CRISPR/Cas9 Using Automata Processing Across Different Platforms. , 2018, , .        |     | 22        |

| 57 | Avoiding cache thrashing due to private data placement in last-level cache for manycore scaling. ,<br>2009, , .                        |     | 21        |

| 58 | Entity resolution acceleration using the automata processor. , 2016, , .                                                               |     | 21        |

| 59 | The Sharing Tracker: Using Ideas from Cache Coherence Hardware to Reduce Off-Chip Memory Traffic with Non-Coherent Caches. , 2010, , . |     | 20        |

| 60 | eAP., 2019,,.                                                                                                                          |     | 20        |

| 61 | Interaction of scaling trends in processor architecture and cooling. , 2010, , .                                                       |     | 19        |

| 62 | Temperature-Aware Architecture: Lessons and Opportunities. IEEE Micro, 2011, 31, 82-86.                                                | 1.8 | 19        |

| 63 | The visual vulnerability spectrum. , 2006, , .                                                                                         |     | 19        |

| 64 | Temperature-to-power mapping. , 2010, , .                                                                                              |     | 18        |

| 65 | BenchFriend. International Journal of High Performance Computing Applications, 2014, 28, 238-250.                                      | 3.7 | 18        |

| 66 | An overview of micron's automata processor. , 2016, , .                                                                                |     | 18        |

| 67 | A Scalable Solution for Rule-Based Part-of-Speech Tagging on Novel Hardware Accelerators. , 2018, , .                                  |     | 18        |

| 68 | Grapefruit: An Open-Source, Full-Stack, and Customizable Automata Processing on FPGAs. , 2020, , .                                     |     | 18        |

| 69 | Accelerated warmup for sampled microarchitecture simulation. Transactions on Architecture and Code Optimization, 2005, 2, 78-108.      | 2.0 | 17        |

| 70 | Real-world design and evaluation of compiler-managed GPU redundant multithreading. Computer<br>Architecture News, 2014, 42, 73-84.     | 2.5 | 17        |

| 71 | Frequent subtree mining on the automata processor. , 2017, , .                                                                         |     | 17        |

| 72 | Characterizing and Mitigating Output Reporting Bottlenecks in Spatial Automata Processing Architectures. , 2018, , .                   |     | 17        |

| #  | Article                                                                                                                                                  | IF                  | CITATIONS            |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|

| 73 | MNCaRT: An Open-Source, Multi-Architecture Automata-Processing Research and Execution Ecosystem.<br>IEEE Computer Architecture Letters, 2018, 17, 84-87. | 1.5                 | 17                   |

| 74 | Fulcrum: A Simplified Control and Access Mechanism Toward Flexible and Practical In-Situ<br>Accelerators. , 2020, , .                                    |                     | 17                   |

| 75 | Robust SIMD: Dynamically Adapted SIMD Width and Multi-Threading Depth. , 2012, , .                                                                       |                     | 15                   |

| 76 | Evaluating Overheads of Multibit Soft-Error Protection in the Processor Core. IEEE Micro, 2013, 33, 56-65.                                               | 1.8                 | 15                   |

| 77 | AutomataZoo: A Modern Automata Processing Benchmark Suite. , 2018, , .                                                                                   |                     | 15                   |

| 78 | FlexAmata: A Universal and Efficient Adaption of Applications to Spatial Automata Processing Accelerators. , 2020, , .                                   |                     | 15                   |

| 79 | Exploiting inter-thread temporal locality for chip multithreading. , 2010, , .                                                                           |                     | 14                   |

| 80 | Tolerating Soft Errors in Processor Cores Using CLEAR (Cross-Layer Exploration for Architecting) Tj ETQqO 0 0 1<br>1839-1852.                            | rgBT /Overlo<br>2.7 | ock 10 Tf 50 4<br>14 |

| 81 | RAPID Programming of Pattern-Recognition Processors. , 2016, , .                                                                                         |                     | 14                   |

| 82 | Enhancing Energy Efficiency in Multi-tier Web Server Clusters via Prioritization. , 2007, , .                                                            |                     | 13                   |

| 83 | Federation. Transactions on Architecture and Code Optimization, 2010, 7, 1-38.                                                                           | 2.0                 | 13                   |

| 84 | Cost-effective safety and fault localization using distributed temporal redundancy. , 2011, , .                                                          |                     | 13                   |

| 85 | Architecture implications of pads as a scarce resource. Computer Architecture News, 2014, 42, 373-384.                                                   | 2.5                 | 13                   |

| 86 | Walking Pads. , 2014, , .                                                                                                                                |                     | 12                   |

| 87 | The resilience wall: Cross-layer solution strategies. , 2014, , .                                                                                        |                     | 12                   |

| 88 | Regular expression acceleration on the micron automata processor: Brill tagging as a case study. , 2015, , .                                             |                     | 12                   |

| 89 | On-Demand Solution to Minimize I-Cache Leakage Energy with Maintaining Performance. IEEE<br>Transactions on Computers, 2008, 57, 7-24.                   | 3.4                 | 11                   |

| 90 | Exploring the thermal impact on manycore processor performance. , 2010, , .                                                                              |                     | 11                   |

| #   | Article                                                                                                                                                        | IF  | CITATIONS |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 91  | Near-Memory Data Services. IEEE Micro, 2016, 36, 6-13.                                                                                                         | 1.8 | 11        |

| 92  | ArchFP: Rapid prototyping of pre-RTL floorplans. , 2012, , .                                                                                                   |     | 10        |

| 93  | ASPEN: A Scalable In-SRAM Architecture for Pushdown Automata. , 2018, , .                                                                                      |     | 10        |

| 94  | GraphTinker: A High Performance Data Structure for Dynamic Graph Processing. , 2019, , .                                                                       |     | 10        |

| 95  | A Scalable and Efficient In-Memory Interconnect Architecture for Automata Processing. IEEE<br>Computer Architecture Letters, 2019, 18, 87-90.                  | 1.5 | 10        |

| 96  | Sieve: Scalable In-situ DRAM-based Accelerator Designs for Massively Parallel k-mer Matching. , 2021, , .                                                      |     | 10        |

| 97  | A Novel Software Solution for Localized Thermal Problems. Lecture Notes in Computer Science, 2006, , 63-74.                                                    | 1.3 | 10        |

| 98  | Hopscotch. , 2019, , .                                                                                                                                         |     | 9         |

| 99  | Alloyed Branch History: Combining Global and Local Branch History for Robust Performance.<br>International Journal of Parallel Programming, 2003, 31, 137-177. | 1.5 | 8         |

| 100 | Generating efficient and high-quality pseudo-random behavior on Automata Processors. , 2016, , .                                                               |     | 8         |

| 101 | Walking pads: Fast power-supply pad-placement optimization. , 2014, , .                                                                                        |     | 7         |

| 102 | Transient voltage noise in charge-recycled power delivery networks for many-layer 3D-IC. , 2015, , .                                                           |     | 7         |

| 103 | Acceleration of Frequent Itemset Mining on FPGA using SDAccel and Vivado HLS. , 2017, , .                                                                      |     | 7         |

| 104 | Automata-to-Routing: An Open-Source Toolchain for Design-Space Exploration of Spatial Automata<br>Processing Architectures. , 2017, , .                        |     | 7         |

| 105 | Automata Processing in Reconfigurable Architectures. ACM Transactions on Reconfigurable Technology and Systems, 2019, 12, 1-25.                                | 2.5 | 7         |

| 106 | PiMulator: a Fast and Flexible Processing-in-Memory Emulation Platform. , 2022, , .                                                                            |     | 7         |

| 107 | Trellis: Portability across architectures with a high-level framework. Journal of Parallel and Distributed Computing, 2013, 73, 1400-1413.                     | 4.1 | 6         |

| 108 | Power-efficient embedded processing with resilience and real-time constraints. , 2015, , .                                                                     |     | 6         |

| #   | Article                                                                                                                                                                    | IF  | CITATIONS |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 109 | A cross-layer design exploration of charge-recycled power-delivery in many-layer 3d-IC. , 2015, , .                                                                        |     | 6         |

| 110 | Debugging Support for Pattern-Matching Languages and Accelerators. , 2019, , .                                                                                             |     | 6         |

| 111 | NOSTalgy: Near-Optimum Run-Time STT-MRAM Quality-Energy Knob Management for Approximate Computing Applications. IEEE Transactions on Computers, 2021, 70, 414-427.         | 3.4 | 6         |

| 112 | A reconfigurable simulator for large-scale heterogeneous multicore architectures. , 2011, , .                                                                              |     | 5         |

| 113 | Yield-aware Performance-Cost Characterization for Multi-Core SIMT. , 2015, , .                                                                                             |     | 5         |

| 114 | Tolerating the Consequences of Multiple EM-Induced C4 Bump Failures. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2016, 24, 2335-2344.             | 3.1 | 5         |

| 115 | Pre-RTL Voltage and Power Optimization for Low-Cost, Thermally Challenged Multicore Chips. , 2017, , .                                                                     |     | 5         |

| 116 | Very Low Voltage (VLV) Design. , 2017, , .                                                                                                                                 |     | 5         |

| 117 | Cross-Layer Resilience. , 2019, , .                                                                                                                                        |     | 5         |

| 118 | Sunder: Enabling Low-Overhead and Scalable Near-Data Pattern Matching Acceleration. , 2021, , .                                                                            |     | 5         |

| 119 | ROCKY: A Robust Hybrid On-chip Memory Kit For The Processors With STT-MRAM Cache Technology.<br>IEEE Transactions on Computers, 2020, , 1-1.                               | 3.4 | 5         |

| 120 | ArchFP: Rapid prototyping of pre-RTL floorplans. , 2012, , .                                                                                                               |     | 4         |

| 121 | Dymaxion++: A Directive-Based API to Optimize Data Layout and Memory Mapping for Heterogeneous Systems. , 2014, , .                                                        |     | 4         |

| 122 | Hierarchical Pattern Mining with the Automata Processor. International Journal of Parallel<br>Programming, 2018, 46, 376-411.                                              | 1.5 | 4         |

| 123 | Towards on-node Machine Learning for Ultra-low-power Sensors Using Asynchronous Σ Δ Streams. ACM<br>Journal on Emerging Technologies in Computing Systems, 2020, 16, 1-20. | 2.3 | 4         |

| 124 | Gearbox. , 2022, , .                                                                                                                                                       |     | 4         |

| 125 | Architectural implications of spatial thermal filtering. The Integration VLSI Journal, 2013, 46, 44-56.                                                                    | 2.1 | 3         |

126 Image classification by multi-kernel dictionary learning. , 2014, , .

| #   | Article                                                                                                                                                                         | IF  | CITATIONS |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 127 | A 16-Bit Reconfigurable Encryption Processor for p-Cipher. , 2016, , .                                                                                                          |     | 3         |

| 128 | Dual-Data Rate Transpose-Memory Architecture Improves the Performance, Power and Area of<br>Signal-Processing Systems. Journal of Signal Processing Systems, 2017, 88, 167-184. | 2.1 | 3         |

| 129 | Cross-Layer Resilience in Low-Voltage Digital Systems: Key Insights. , 2017, , .                                                                                                |     | 3         |

| 130 | RAPID Programming of Pattern-Recognition Processors. Operating Systems Review (ACM), 2016, 50, 593-605.                                                                         | 1.9 | 3         |

| 131 | Accelerating Weeder: A DNA Motif Search Tool Using the Micron Automata Processor and FPGA. IEICE<br>Transactions on Information and Systems, 2017, E100.D, 2470-2477.           | 0.7 | 3         |

| 132 | Thermal benefit of multi-core floorplanning: A limits study. Sustainable Computing: Informatics and Systems, 2011, 1, 286-293.                                                  | 2.2 | 2         |

| 133 | A meta-algorithm for classification by feature nomination. , 2014, , .                                                                                                          |     | 2         |

| 134 | Lumos+: Rapid, pre-RTL design space exploration on accelerator-rich heterogeneous architectures with reconfigurable logic. , 2016, , .                                          |     | 2         |

| 135 | Feature extraction and image retrieval on an automata structure. , 2016, , .                                                                                                    |     | 2         |

| 136 | Classifying images in a histopathological dataset using the cumulative distribution transform on an automata architecture. , 2017, , .                                          |     | 2         |

| 137 | PPE-ARX: Area- and power-efficient VLIW programmable processing element for IoT crypto-systems. , 2017, , .                                                                     |     | 2         |

| 138 | Portable Programming with RAPID. IEEE Transactions on Parallel and Distributed Systems, 2019, 30, 939-952.                                                                      | 5.6 | 2         |

| 139 | MTTF Enhancement Power-C4 Bump Placement Optimization. IEEE Transactions on Very Large Scale<br>Integration (VLSI) Systems, 2019, 27, 1633-1639.                                | 3.1 | 2         |

| 140 | Reco-Pi: A reconfigurable Cryptoprocessor for π-Cipher. Journal of Parallel and Distributed Computing, 2019, 133, 420-431.                                                      | 4.1 | 2         |

| 141 | Enabling In-SRAM Pattern Processing With Low-Overhead Reporting Architecture. IEEE Computer<br>Architecture Letters, 2020, 19, 167-170.                                         | 1.5 | 2         |

| 142 | RAPID Programming of Pattern-Recognition Processors. ACM SIGPLAN Notices, 2016, 51, 593-605.                                                                                    | 0.2 | 2         |

| 143 | Design and Implementation of an Energy Efficient Multimedia Playback System. , 2006, , .                                                                                        |     | 1         |

| 144 | Low-Power Design and Temperature Management. IEEE Micro, 2007, 27, 46-57.                                                                                                       | 1.8 | 1         |

| #   | Article                                                                                                                                                       | IF  | CITATIONS |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 145 | Editorial: Letter from the Editor-in-Chief. IEEE Computer Architecture Letters, 2011, 10, 1-3.                                                                | 1.5 | 1         |

| 146 | Closing the power delivery/heat removal cycle for heterogeneous multi-scale systems. , 2016, , .                                                              |     | 1         |

| 147 | BigMap: Future-proofing Fuzzers with Efficient Large Maps. , 2021, , .                                                                                        |     | 1         |

| 148 | RAPID Programming of Pattern-Recognition Processors. Computer Architecture News, 2016, 44, 593-605.                                                           | 2.5 | 1         |

| 149 | Small-scale reconfigurability for improved performance and double-precision in graphics hardware.<br>International Journal of Electronics, 2007, 94, 549-561. | 1.4 | 0         |

| 150 | Editorial: Letter from the Editor-in-Chief. IEEE Computer Architecture Letters, 2010, 9, 37-44.                                                               | 1.5 | 0         |

| 151 | Introducing the New Editor-in-Chief of the IEEE Computer Architecture Letters. IEEE Computer Architecture Letters, 2013, 12, 1-1.                             | 1.5 | 0         |

| 152 | Thermal Modeling for Processors and Systems-on-Chip. , 2010, , 243-257.                                                                                       |     | 0         |

| 153 | Edge Crypt-Pi: Securing Internet of Things with Light and Fast Crypto-Processor. Advances in Intelligent Systems and Computing, 2021, , 749-761.              | 0.6 | 0         |

| 154 | Supporting Moderate Data Dependency, Position Dependency, and Divergence in PIM-based Accelerators. IEEE Micro, 2022, , 1-1.                                  | 1.8 | 0         |

| 155 | Synthesizing Legacy String Code for FPGAs Using Bounded Automata Learning. IEEE Micro, 2022, 42, 70-77.                                                       | 1.8 | 0         |