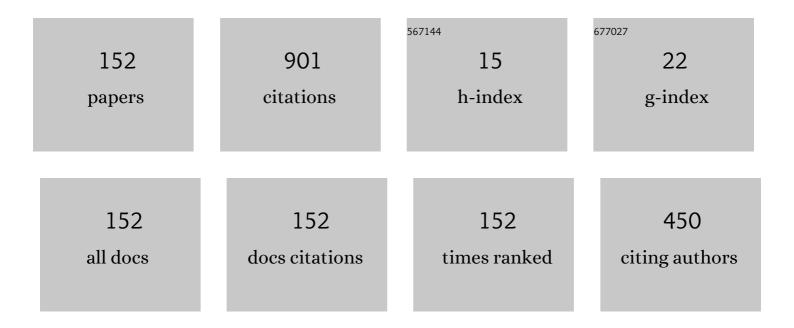

## Wooheon Kang

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/5790406/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                                                  | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | Novel Error-Tolerant Voltage-Divider-Based Through-Silicon-Via Test Architecture. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2023, 42, 308-321.      | 1.9 | 0         |

| 2  | Multibank Optimized Redundancy Analysis Using Efficient Fault Collection. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41, 2739-2752.            | 1.9 | 2         |

| 3  | Herringbone-Based TSV Architecture for Clustered Fault Repair and Aging Recovery. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41, 1142-1153.    | 1.9 | 3         |

| 4  | Reduced-Pin-Count BOST for Test-Cost Reduction. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41, 750-761.                                        | 1.9 | 3         |

| 5  | SPAR: A New Test-Point Insertion Using Shared Points for Area Overhead Reduction. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41, 4939-4951.    | 1.9 | 2         |

| 6  | A Hybrid Test Scheme for Automotive IC in Multi-site Testing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, , 1-1.                                | 1.9 | 0         |

| 7  | ECMO: ECC Architecture Reusing Content-Addressable Memories for Obtaining High Reliability in DRAM. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2022, 30, 781-793. | 2.1 | 1         |

| 8  | On-Chip Error Detection Reusing Built-In Self-Repair for Silicon Debug. IEEE Access, 2021, 9, 56443-56456.                                                                               | 2.6 | 5         |

| 9  | Effective Spare Line Allocation Built-in Redundancy Analysis With Base Common Spare for Yield<br>Improvement of 3D Memory. IEEE Access, 2021, 9, 76716-76729.                            | 2.6 | 0         |

| 10 | An In-DRAM BIST for 16 Gb DDR4 DRAM in the 2nd 10-nm-Class DRAM Process. IEEE Access, 2021, 9, 33487-33497.                                                                              | 2.6 | 7         |

| 11 | ECC-Aware Fast and Reliable Pattern Matching Redundancy Analysis for Highly Reliable Memory. IEEE<br>Access, 2021, 9, 133274-133288.                                                     | 2.6 | 0         |

| 12 | Reconfigurable Scan Architecture for High Diagnostic Resolution. IEEE Access, 2021, 9, 120537-120550.                                                                                    | 2.6 | 3         |

| 13 | Enhanced Postbond Test Architecture for Bridge Defects Between the TSVs. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2021, 29, 1164-1177.                       | 2.1 | 3         |

| 14 | A Secure Scan Architecture Protecting Scan Test and Scan Dump Using Skew-Based Lock and Key. IEEE<br>Access, 2021, 9, 102161-102176.                                                     | 2.6 | 2         |

| 15 | Low-Power Scan Correlation-Aware Scan Cluster Reordering for Wireless Sensor Networks. Sensors, 2021, 21, 6111.                                                                          | 2.1 | 1         |

| 16 | A Circular-based TSV Repair Architecture. , 2021, , .                                                                                                                                    |     | 1         |

| 17 | Area Efficient Built-In Redundancy Analysis using Pre-Solutions with Various Spare Structure. , 2021, , .                                                                                |     | 0         |

| 18 | An Effective Spare Allocation Methodology for 3D Memory Repair with BIRA. , 2021, , .                                                                                                    |     | 0         |

| #  | Article                                                                                                                                                                                         | IF  | CITATIONS |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | Hardware Efficient Built-in Self-test Architecture for Power and Ground TSVs in 3D IC. , 2021, , .                                                                                              |     | 2         |

| 20 | A 3-D Rotation-Based Through-Silicon via Redundancy Architecture for Clustering Faults. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2020, 39, 1925-1934.  | 1.9 | 8         |

| 21 | GPU-Based Redundancy Analysis Using Concurrent Evaluation. IEEE Transactions on Very Large Scale<br>Integration (VLSI) Systems, 2020, 28, 805-817.                                              | 2.1 | 4         |

| 22 | Robust Secure Shield Architecture for Detection and Protection Against Invasive Attacks. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2020, 39, 3023-3034. | 1.9 | 9         |

| 23 | A New Logic Topology-Based Scan Chain Stitching for Test-Power Reduction. IEEE Transactions on Circuits and Systems II: Express Briefs, 2020, 67, 3432-3436.                                    | 2.2 | 5         |

| 24 | Prediction-Based Error Correction for GPU Reliability with Low Overhead. Electronics (Switzerland), 2020, 9, 1849.                                                                              | 1.8 | 2         |

| 25 | W-ERA: One-Time Memory Repair with Wafer-Level Early Repair Analysis for Cost Reduction. , 2020, , .                                                                                            |     | 0         |

| 26 | Fine-Grained Defect Diagnosis for CMOL FPGA Circuits. IEEE Access, 2020, 8, 163140-163151.                                                                                                      | 2.6 | 0         |

| 27 | Scan-Chain-Fault Diagnosis Using Regressions in Cryptographic Chips for Wireless Sensor Networks.<br>Sensors, 2020, 20, 4771.                                                                   | 2.1 | 4         |

| 28 | Advanced Low Pin Count Test Architecture for Efficient Multi-Site Testing. IEEE Transactions on Semiconductor Manufacturing, 2020, 33, 391-403.                                                 | 1.4 | 3         |

| 29 | Redundancy Analysis Optimization with Clustered Known Solutions for High Speed Repair. , 2020, , .                                                                                              |     | 0         |

| 30 | Fail Memory Configuration Set for RA Estimation. , 2020, , .                                                                                                                                    |     | 7         |

| 31 | Highly Reliable Redundant TSV Architecture for Clustered Faults. IEEE Transactions on Reliability, 2019, 68, 237-247.                                                                           | 3.5 | 12        |

| 32 | TSV Repair Architecture for Clustered Faults. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2019, 38, 190-194.                                                 | 1.9 | 8         |

| 33 | Test-Friendly Data-Selectable Self-Gating (DSSG). IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019, 27, 1972-1976.                                                        | 2.1 | 3         |

| 34 | Dynamic Built-In Redundancy Analysis for Memory Repair. IEEE Transactions on Very Large Scale<br>Integration (VLSI) Systems, 2019, 27, 2365-2374.                                               | 2.1 | 11        |

| 35 | A low-cost concurrent TSV test architecture with lossless test output compression scheme. PLoS ONE, 2019, 14, e0221043.                                                                         | 1.1 | 5         |

| 36 | An Efficient BIRA Utilizing Characteristics of Spare Pivot Faults. IEEE Transactions on Computer-Aided<br>Design of Integrated Circuits and Systems, 2019, 38, 551-561.                         | 1.9 | 5         |

| #  | Article                                                                                                                                                                                                  | lF  | CITATIONS |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 37 | Fast Built-In Redundancy Analysis Based on Sequential Spare Line Allocation. IEEE Transactions on Reliability, 2018, 67, 264-273.                                                                        | 3.5 | 10        |

| 38 | Fault Group Pattern Matching With Efficient Early Termination for High-Speed Redundancy Analysis.<br>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2018, 37, 1473-1482. | 1.9 | 13        |

| 39 | Thermal Aware Test Scheduling for NTV Circuit. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2018, 37, 906-910.                                                         | 1.9 | 2         |

| 40 | Neural Network Reliability Enhancement Approach Using Dropout Underutilization in GPU. , 2018, , .                                                                                                       |     | 0         |

| 41 | 2-D Failure Bitmap Compression Using Line Fault Marking Method. , 2018, , .                                                                                                                              |     | 1         |

| 42 | 3D Memory Formed of Unrepairable Memory Dice and Spare Layer. , 2018, , .                                                                                                                                |     | 0         |

| 43 | A debug scheme to improve the error identification in post-silicon validation. PLoS ONE, 2018, 13, e0202216.                                                                                             | 1.1 | 1         |

| 44 | An Area-Efficient BIRA With 1-D Spare Segments. IEEE Transactions on Very Large Scale Integration<br>(VLSI) Systems, 2018, 26, 206-210.                                                                  | 2.1 | 5         |

| 45 | Test Resource Reused Debug Scheme to Reduce the Post-Silicon Debug Cost. IEEE Transactions on Computers, 2018, 67, 1835-1839.                                                                            | 2.4 | 2         |

| 46 | A Statistic-Based Scan Chain Reordering for Energy-Quality Scalable Scan Test. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2018, 8, 391-403.                                   | 2.7 | 3         |

| 47 | An On-Chip Error Detection Method to Reduce the Post-Silicon Debug Time. IEEE Transactions on Computers, 2017, 66, 38-44.                                                                                | 2.4 | 7         |

| 48 | FRESH: A New Test Result Extraction Scheme for Fast TSV Tests. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2017, 36, 336-345.                                         | 1.9 | 4         |

| 49 | Off-chip test architecture for improving multi-site testing efficiency using tri-state decoder and<br>3V-level encoder. , 2017, , .                                                                      |     | 2         |

| 50 | R <sup>2</sup> -TSV: A Repairable and Reliable TSV Set Structure Reutilizing Redundancies. IEEE<br>Transactions on Reliability, 2017, 66, 458-466.                                                       | 3.5 | 17        |

| 51 | DRAM-Based Error Detection Method to Reduce the Post-Silicon Debug Time for Multiple Identical<br>Cores. IEEE Transactions on Computers, 2017, 66, 1504-1517.                                            | 2.4 | 6         |

| 52 | Hardware-Efficient Built-In Redundancy Analysis for Memory With Various Spares. IEEE Transactions<br>on Very Large Scale Integration (VLSI) Systems, 2017, 25, 844-856.                                  | 2.1 | 20        |

| 53 | Grouping-Based TSV Test Architecture for Resistive Open and Bridge Defects in 3-D-ICs. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2017, 36, 1759-1763.            | 1.9 | 11        |

| 54 | Chain-Based Approach for Fast Through-Silicon-Via Coupling Delay Estimation. IEEE Transactions on<br>Very Large Scale Integration (VLSI) Systems, 2017, 25, 1178-1182.                                   | 2.1 | 1         |

| #  | Article                                                                                                                                                                                        | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 55 | Proof of Concept of Home IoT Connected Vehicles. Sensors, 2017, 17, 1289.                                                                                                                      | 2.1 | 20        |

| 56 | LARECD: Low area overhead and reliable error correction DMR architecture. , 2017, , .                                                                                                          |     | 2         |

| 57 | An efficient built-in self-repair scheme for area reduction. , 2017, , .                                                                                                                       |     | 3         |

| 58 | Reconfigurable scan architecture for test power and data volume reduction. IEICE Electronics Express, 2017, 14, 20170415-20170415.                                                             | 0.3 | 2         |

| 59 | A novel X-filling method for capture power reduction. IEICE Electronics Express, 2017, 14, 20171093-20171093.                                                                                  | 0.3 | Ο         |

| 60 | A low-cost DAC BIST structure using a resistor loop. PLoS ONE, 2017, 12, e0172331.                                                                                                             | 1.1 | 0         |

| 61 | A TSV test structure for simultaneously detecting resistive open and bridge defects in 3D-ICs. , 2016, , .                                                                                     |     | 9         |

| 62 | Discussion of cost-effective redundancy architectures. , 2016, , .                                                                                                                             |     | 0         |

| 63 | Test access mechaism for stack test time reduction of 3-dimensional integrated circuit. , 2016, , .                                                                                            |     | Ο         |

| 64 | A New3-D Fuse Architecture to Improve Yield of 3-D Memories. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2016, , 1-1.                                       | 1.9 | 0         |

| 65 | Parallelized Network-on-Chip-Reused Test Access Mechanism for Multiple Identical Cores. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2016, 35, 1219-1223. | 1.9 | 2         |

| 66 | Tri-State Coding Using Reconfiguration of Twisted Ring Counter for Test Data Compression. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2016, 35, 274-284. | 1.9 | 7         |

| 67 | Reduced-code test method using sub-histograms for pipelined ADCs. IEICE Electronics Express, 2015, 12, 20150417-20150417.                                                                      | 0.3 | Ο         |

| 68 | Fully Programmable Memory BIST for Commodity DRAMs. ETRI Journal, 2015, 37, 787-792.                                                                                                           | 1.2 | 2         |

| 69 | Failure bitmap compression method for 3D-IC redundancy analysis. , 2015, , .                                                                                                                   |     | Ο         |

| 70 | A 2-D compaction method using macro block for post-silicon validation. , 2015, , .                                                                                                             |     | 3         |

| 71 | Eco Assist Techniques through Real-time Monitoring of BEV Energy Usage Efficiency. Sensors, 2015, 15, 14946-14959.                                                                             | 2.1 | 7         |

| 72 | New Thermal-Aware Voltage Island Formation for 3D Many-Core Processors. ETRI Journal, 2015, 37, 118-127.                                                                                       | 1.2 | 1         |

| #  | Article                                                                                                                                                                                                               | IF  | CITATIONS |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 73 | Scan Chain Reordering-Aware X-Filling and Stitching for Scan Shift Power Reduction. , 2015, , .                                                                                                                       |     | 15        |

| 74 | A new built-in redundancy analysis algorithm based on multiple memory blocks. , 2015, , .                                                                                                                             |     | 3         |

| 75 | Optimized Built-In Self-Repair for Multiple Memories. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, , 1-10.                                                                                 | 2.1 | 8         |

| 76 | Low power scan bypass technique with test data reduction. , 2015, , .                                                                                                                                                 |     | 2         |

| 77 | A 3 Dimensional Built-In Self-Repair Scheme for Yield Improvement of 3 Dimensional Memories. IEEE<br>Transactions on Reliability, 2015, 64, 586-595.                                                                  | 3.5 | 18        |

| 78 | A Novel Massively Parallel Testing Method Using Multi-Root for High Reliability. IEEE Transactions on Reliability, 2015, 64, 486-496.                                                                                 | 3.5 | 12        |

| 79 | 3-D Stacked DRAM Refresh Management With Guaranteed Data Reliability. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2015, 34, 1455-1466.                                             | 1.9 | 5         |

| 80 | A scan shifting method based on clock gating of multiple groups for low power scan testing. , 2015, , .                                                                                                               |     | 11        |

| 81 | A New Accelerated Endurance Test for Terabit NAND Flash Memory Using Interference Effect. IEEE<br>Transactions on Semiconductor Manufacturing, 2015, 28, 399-407.                                                     | 1.4 | 6         |

| 82 | Histogram-Based Calibration Method for Pipeline ADCs. PLoS ONE, 2015, 10, e0129736.                                                                                                                                   | 1.1 | 0         |

| 83 | A Scalable and Parallel Test Access Strategy for NoC-Based Multicore System. , 2014, , .                                                                                                                              |     | 8         |

| 84 | A new redundancy analysis algorithm using one side pivot. , 2014, , .                                                                                                                                                 |     | 6         |

| 85 | A Delay Test Architecture for TSV With Resistive Open Defects in 3-D Stacked Memories. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22, 2380-2387.                                      | 2.1 | 21        |

| 86 | A BIRA for Memories With an Optimal Repair Rate Using Spare Memories for Area Reduction. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22, 2336-2349.                                    | 2.1 | 25        |

| 87 | Interleaving Test Algorithm for Subthreshold Leakage-Current Defects in DRAM Considering the Equal<br>Bit Line Stress. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22, 803-812.           | 2.1 | 2         |

| 88 | A New Fuse Architecture and a New Post-Share Redundancy Scheme for Yield Enhancement in<br>3-D-Stacked Memories. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,<br>2014, 33, 786-797. | 1.9 | 13        |

| 89 | Reducing the failure bitmap size with a partial solution search tree for the low cost automatic test equipment (ATE). , 2014, , .                                                                                     |     | 0         |

| 90 | Recovery-enhancing task scheduling for multicore processors under NBTI impact. IEICE Electronics Express, 2014, 11, 20140324-20140324.                                                                                | 0.3 | 0         |

| #   | Article                                                                                                                                                                                                                                                  | IF  | CITATIONS |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 91  | Bit transmission error correction scheme for FlexRay based automotive communication systems. , 2013, , .                                                                                                                                                 |     | 1         |

| 92  | A new TSV set architecture for high reliability. , 2013, , .                                                                                                                                                                                             |     | 1         |

| 93  | An efficient RPCT (Reduced Pin Count Testing) based on test data compression using burst clock controller in 3D-IC. , 2013, , .                                                                                                                          |     | 1         |

| 94  | Test scheduling using Ant Colony Optimization for 3D integrated circuits. , 2013, , .                                                                                                                                                                    |     | 0         |

| 95  | Thermal-aware dynamic voltage frequency scaling for many-core processors under process variations. IEICE Electronics Express, 2013, 10, 20130463-20130463.                                                                                               | 0.3 | 6         |

| 96  | Dynamic thermal management for 3D multicore processors under process variations. IEICE<br>Electronics Express, 2013, 10, 20130800-20130800.                                                                                                              | 0.3 | 0         |

| 97  | A Fast Redundancy Analysis Algorithm in ATE for Repairing Faulty Memories. ETRI Journal, 2012, 34, 478-481.                                                                                                                                              | 1.2 | 7         |

| 98  | Integration of dual channel timing formatter system for high speed memory test equipment. , 2012, , .                                                                                                                                                    |     | 9         |

| 99  | Yield Enhancement Techniques for 3D Memories by Redundancy Sharing among All Layers. ETRI Journal, 2012, 34, 388-398.                                                                                                                                    | 1.2 | 3         |

| 100 | A new static test of a DAC with a built-in structure. , 2011, , .                                                                                                                                                                                        |     | 0         |

| 101 | An ant colony optimization approach for the preference-based shortest path search. Journal of the<br>Chinese Institute of Engineers, Transactions of the Chinese Institute of Engineers,Series A/Chung-kuo<br>Kung Ch'eng Hsuch K'an, 2011, 34, 181-196. | 0.6 | 11        |

| 102 | A low-cost DDEM ADC structure for the testing of high-performance DACs. , 2011, , .                                                                                                                                                                      |     | 2         |

| 103 | New Fault Detection Algorithm for Multi-level Cell Flash Memroies. , 2011, , .                                                                                                                                                                           |     | 1         |

| 104 | A Lossless Color Image Compression Architecture Using a Parallel Golomb-Rice Hardware CODEC. IEEE<br>Transactions on Circuits and Systems for Video Technology, 2011, 21, 1581-1587.                                                                     | 5.6 | 23        |

| 105 | A new scan slice encoding scheme with flexible code for test data compression. , 2010, , .                                                                                                                                                               |     | 0         |

| 106 | A Pattern Group Partitioning for Parallel String Matching using a Pattern Grouping Metric. IEEE<br>Communications Letters, 2010, 14, 878-880.                                                                                                            | 2.5 | 11        |

| 107 | EOF: Efficient Built-In Redundancy Analysis Methodology With Optimal Repair Rate. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2010, 29, 1130-1135.                                                                    | 1.9 | 14        |

| 108 | An Advanced BIRA for Memories With an Optimal Repair Rate and Fast Analysis Speed by Using a Branch<br>Analyzer. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2010, 29,<br>2014-2026.                                  | 1.9 | 48        |

| #   | Article                                                                                                                                                                                                                              | IF  | CITATIONS |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 109 | FiX-compact: A new X-tolerant response compaction scheme for fixed unknown logic values. , 2010, , .                                                                                                                                 |     | 1         |

| 110 | An area efficient programmable built-in self-test for embedded memories using an extended address counter. , 2010, , .                                                                                                               |     | 3         |

| 111 | DFT for achieving hybrid transiton delay fault test with Reduced Pin Count Testing. , 2009, , .                                                                                                                                      |     | 0         |

| 112 | A BIST architecture for multiple DACs in an LTPS TFT-LCD source driver IC. , 2009, , .                                                                                                                                               |     | 2         |

| 113 | A hardware-efficent multi-character string matching architecture using brute-force algorithm. , 2009, , .                                                                                                                            |     | 7         |

| 114 | An Efficient Hardware Architecture of the A-star Algorithm for the Shortest Path Search Engine. ,<br>2009, , .                                                                                                                       |     | 19        |

| 115 | An Advanced BIRA using parallel sub-analyzers for embedded memories. , 2009, , .                                                                                                                                                     |     | 6         |

| 116 | A High-Level Signal Integrity Fault Model and Test Methodology for Long On-Chip Interconnections. ,<br>2009, , .                                                                                                                     |     | 0         |

| 117 | A Fast Built-in Redundancy Analysis for Memories With Optimal Repair Rate Using a Line-Based Search<br>Tree. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2009, 17, 1665-1678.                                  | 2.1 | 51        |

| 118 | ATPG-XP: Test Generation for Maximal Crosstalk-Induced Faults. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2009, 28, 1401-1413.                                                                   | 1.9 | 16        |

| 119 | A memory-efficient parallel string matching for intrusion detection systems. IEEE Communications<br>Letters, 2009, 13, 1004-1006.                                                                                                    | 2.5 | 16        |

| 120 | FPGA-based verification methodology of SoC-type CMOS image signal processor. , 2009, , .                                                                                                                                             |     | 1         |

| 121 | Selective scan slice repetition for simultaneous reduction of test power consumption and test data volume. IEICE Electronics Express, 2009, 6, 1432-1437.                                                                            | 0.3 | 5         |

| 122 | An Effective Programmable Memory BIST for Embedded Memory. IEICE Transactions on Information and Systems, 2009, E92-D, 2508-2511.                                                                                                    | 0.4 | 8         |

| 123 | A New Scan Architecture for Both Low Power Testing and Test Volume Compression Under SOC Test Environment. Journal of Electronic Testing: Theory and Applications (JETTA), 2008, 24, 365-378.                                        | 0.9 | 6         |

| 124 | An Effective Power Reduction Methodology for Deterministic BIST Using Auxiliary LFSR. Journal of Electronic Testing: Theory and Applications (JETTA), 2008, 24, 591-595.                                                             | 0.9 | 1         |

| 125 | An Effective Hybrid Test Data Compression Method Using Scan Chain Compaction and Dictionary-Based Scheme. , 2008, , .                                                                                                                |     | 2         |

| 126 | Total Energy Minimization of Real-Time Tasks in an On-Chip Multiprocessor Using Dynamic Voltage<br>Scaling Efficiency Metric. IEEE Transactions on Computer-Aided Design of Integrated Circuits and<br>Systems, 2008, 27, 2088-2092. | 1.9 | 18        |

| #   | Article                                                                                                                                                                    | IF  | CITATIONS |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 127 | An Efficient Scan Chain Diagnosis Method Using a New Symbolic Simulation. VLSI Test Symposium (VTS),<br>Proceedings, IEEE, 2008, , .                                       | 1.0 | 3         |

| 128 | XPDF-ATPG: An Efficient Test Pattern Generation for Crosstalk-Induced Faults. , 2008, , .                                                                                  |     | 0         |

| 129 | Variable-length block nine-coded compression technique with Huffman codes and symbol merging. , 2008, , .                                                                  |     | 0         |

| 130 | A New Wafer Level Latent Defect Screening Methodology for Highly Reliable DRAM Using a Response<br>Surface Method. , 2008, , .                                             |     | 0         |

| 131 | An effective parallel ALPG using instruction unrolling for high speed memory testing. , 2008, , .                                                                          |     | 2         |

| 132 | A Prevenient Voltage Stress Test Method for High Density Memory. , 2008, , .                                                                                               |     | 0         |

| 133 | Ant colony based efficient triplet calculation methodology for arithmetic built-in self test. IEICE<br>Electronics Express, 2008, 5, 877-881.                              | 0.3 | 0         |

| 134 | Path delay fault diagnosis using path scoring. , 2008, , .                                                                                                                 |     | 2         |

| 135 | High-MDSI: A High-level Signal Integrity Fault Test Pattern Generation Method for Interconnects. , 2007, , .                                                               |     | 3         |

| 136 | MDSI: Signal Integrity Interconnect Fault Modeling and Testing for SoCs. Journal of Electronic Testing: Theory and Applications (JETTA), 2007, 23, 357-362.                | 0.9 | 18        |

| 137 | High-MDSI: A High-level Signal Integrity Fault Test Pattern Generation Method for Interconnects.<br>Proceedings of the Asian Test Symposium, 2007, , .                     | 0.0 | 0         |

| 138 | An Effective Test Pattern Generation for Testing Signal Integrity. Proceedings of the Asian Test<br>Symposium, 2006, , .                                                   | 0.0 | 0         |

| 139 | MICRO: a new hybrid test data compression/decompression scheme. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2006, 14, 649-654.                       | 2.1 | 3         |

| 140 | TOSCA: Total Scan Power Reduction Architecture based on Pseudo-Random Built-in Self Test<br>Structure. Proceedings of the Asian Test Symposium, 2006, , .                  | 0.0 | 0         |

| 141 | Increasing encoding efficiency of LFSR reseeding-based test compression. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25, 913-917. | 1.9 | 24        |

| 142 | An Efficient Dictionary Organization for Maximum Diagnosis. Journal of Electronic Testing: Theory and Applications (JETTA), 2006, 22, 37-48.                               | 0.9 | 0         |

| 143 | A New Low Power Test Pattern Generator using a Transition Monitoring Window based on BIST Architecture. , 2005, , .                                                        |     | 3         |

| 144 | Code-Width Testing-Based Compact ADC BIST Circuit. IEEE Transactions on Circuits and Systems Part 2:<br>Express Briefs, 2004, 51, 603-606.                                 | 2.3 | 29        |

| #   | Article                                                                                                                                                                | IF  | CITATIONS |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 145 | A new maximal diagnosis algorithm for interconnect test. IEEE Transactions on Very Large Scale<br>Integration (VLSI) Systems, 2004, 12, 532-537.                       | 2.1 | 14        |

| 146 | New Distributed Arithmetic Algorithm for Low-Power FIR Filter Implementation. IEEE Signal Processing Letters, 2004, 11, 463-466.                                       | 2.1 | 35        |

| 147 | Test-decompression mechanism using a variable-length multiple-polynomial LFSR. IEEE Transactions on<br>Very Large Scale Integration (VLSI) Systems, 2003, 11, 687-690. | 2.1 | 12        |

| 148 | At-speed boundary-scan interconnect testing in a board with multiple system clocks. , 0, , .                                                                           |     | 0         |

| 149 | A new maximal diagnosis algorithm for bus-structured systems. , 0, , .                                                                                                 |     | 0         |

| 150 | A new maximal diagnosis algorithm for bus-structured systems. , 0, , .                                                                                                 |     | 0         |

| 151 | RAIN (RAndom Insertion) Scheduling Algorithm for SoC Test. , 0, , .                                                                                                    |     | 5         |

| 152 | An efficient all-digital built-in self-test for chargepump PLL. , 0, , .                                                                                               |     | 9         |