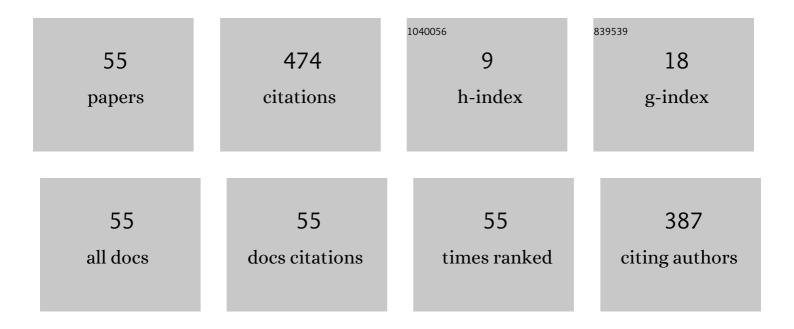

## Francesca Palumbo

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/5341510/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                                                          | IF  | CITATIONS |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | An Off-the-Shelf Instant Contact Casting Device for the Management of Diabetic Foot Ulcers: A randomized prospective trial versus traditional fiberglass cast. Diabetes Care, 2007, 30, 586-590. | 8.6 | 108       |

| 2  | An FPGA Platform for Real-Time Simulation of Spiking Neuronal Networks. Frontiers in Neuroscience, 2017, 11, 90.                                                                                 | 2.8 | 69        |

| 3  | The FitOptiVis ECSEL project. , 2019, , .                                                                                                                                                        |     | 28        |

| 4  | The multi-dataflow composer tool: generation of on-the-fly reconfigurable platforms. Journal of Real-Time Image Processing, 2014, 9, 233-249.                                                    | 3.5 | 21        |

| 5  | An integrated hardware/software design methodology for signal processing systems. Journal of<br>Systems Architecture, 2019, 93, 1-19.                                                            | 4.3 | 18        |

| 6  | Challenging the Best HEVC Fractional Pixel FPGA Interpolators With Reconfigurable and Multifrequency Approximate Computing. IEEE Embedded Systems Letters, 2017, 9, 65-68.                       | 1.9 | 15        |

| 7  | Automated Design Flow for Multi-Functional Dataflow-Based Platforms. Journal of Signal Processing Systems, 2016, 85, 143-165.                                                                    | 2.1 | 14        |

| 8  | Power-Awarness in Coarse-Grained Reconfigurable Multi-Functional Architectures: a Dataflow Based Strategy. Journal of Signal Processing Systems, 2017, 87, 81-106.                               | 2.1 | 14        |

| 9  | The Multi-Dataflow Composer tool: A runtime reconfigurable HDL platform composer. , 2011, , .                                                                                                    |     | 13        |

| 10 | DSE and profiling of multi-context coarse-grained reconfigurable systems. , 2013, , .                                                                                                            |     | 13        |

| 11 | A coarse-grained reconfigurable approach for low-power spike sorting architectures. , 2013, , .                                                                                                  |     | 13        |

| 12 | Coarseâ€grained reconfiguration: dataflowâ€based power management. IET Computers and Digital<br>Techniques, 2015, 9, 36-48.                                                                      | 1.2 | 12        |

| 13 | Optimization and deployment of CNNs at the edge. , 2019, , .                                                                                                                                     |     | 10        |

| 14 | Quantum Correlations in a Generalized Spin Star System. Open Systems and Information Dynamics, 2006, 13, 309-314.                                                                                | 1.2 | 9         |

| 15 | Reconfigurable coprocessors synthesis in the MPEC-RVC domain. , 2015, , .                                                                                                                        |     | 8         |

| 16 | Power and clock gating modelling in coarse grained reconfigurable systems. , 2016, , .                                                                                                           |     | 8         |

| 17 | Automated power gating methodology for dataflow-based reconfigurable systems. , 2015, , .                                                                                                        |     | 6         |

| 18 | Dataflow-Functional High-Level Synthesis for Coarse-Grained Reconfigurable Accelerators. IEEE<br>Embedded Systems Letters, 2019, 11, 69-72.                                                      | 1.9 | 6         |

Francesca Palumbo

| #  | Article                                                                                                                                                                                              | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | The Multi-Dataflow Composer tool: An open-source tool suite for optimized coarse-grain reconfigurable hardware accelerators and platform design. Microprocessors and Microsystems, 2021, 80, 103326. | 2.8 | 6         |

| 20 | Runtime Energy versus Quality Tuning in Motion Compensation Filters for HEVC. IFAC-PapersOnLine, 2016, 49, 145-152.                                                                                  | 0.9 | 5         |

| 21 | Hardware design methodology using lightweight dataflow and its integration with low power techniques. Journal of Systems Architecture, 2017, 78, 15-29.                                              | 4.3 | 5         |

| 22 | Design and management of image processing pipelines within CPS: 2 years of experience from the FitOptiVis ECSEL Project. , 2020, , .                                                                 |     | 5         |

| 23 | A Novel Non-exclusive Dual-Mode Architecture for MPSoCs-Oriented Network on Chip Designs.<br>Lecture Notes in Computer Science, 2008, , 96-105.                                                      | 1.3 | 5         |

| 24 | A Surface Tension and Coalescence Model for Dynamic Distributed Resources Allocation in Massively<br>Parallel Processors on-Chip. Studies in Computational Intelligence, 2008, , 335-345.            | 0.9 | 5         |

| 25 | MPSoCs for real-time neural signal decoding: A low-power ASIP-based implementation.<br>Microprocessors and Microsystems, 2016, 43, 67-80.                                                            | 2.8 | 4         |

| 26 | Hardware/Software Self-adaptation in CPS: The CERBERO Project Approach. Lecture Notes in Computer Science, 2019, , 416-428.                                                                          | 1.3 | 4         |

| 27 | CERBERO: Cross-layer modEl-based fRamework for multi-oBjective dEsign of reconfigurable systems in unceRtain hybRid envirOnments. , 2019, , .                                                        |     | 4         |

| 28 | NeuPow. , 2019, , .                                                                                                                                                                                  |     | 4         |

| 29 | Unmanned Vehicles in Smart Farming: a Survey and a Glance at Future Horizons. , 2021, , .                                                                                                            |     | 4         |

| 30 | Power-awarness in coarse-grained reconfigurable designs: A dataflow based strategy. , 2014, , .                                                                                                      |     | 3         |

| 31 | Modelling and Automated Implementation of Optimal Power Saving Strategies in Coarse-Grained Reconfigurable Architectures. Journal of Electrical and Computer Engineering, 2016, 2016, 1-27.          | 0.9 | 3         |

| 32 | On-the-fly adaptivity for process networks over shared-memory platforms. Microprocessors and Microsystems, 2016, 46, 240-254.                                                                        | 2.8 | 3         |

| 33 | Adaptable AES implementation with power-gating support. , 2016, , .                                                                                                                                  |     | 3         |

| 34 | Multi-Grain Reconfiguration for Advanced Adaptivity in Cyber-Physical Systems. , 2018, , .                                                                                                           |     | 3         |

| 35 | Design and management of image processing pipelines within CPS: Acquired experience towards the end of the FitOptiVis ECSEL Project. Microprocessors and Microsystems, 2021, 87, 104350.             | 2.8 | 3         |

| 36 | Automatic generation of dataflow-based reconfigurable co-processing units. , 2014, , .                                                                                                               |     | 2         |

Francesca Palumbo

| #  | Article                                                                                                                                                                  | IF  | CITATIONS |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 37 | Exploring custom heterogeneous MPSoCs for real-time neural signal decoding. , 2015, , .                                                                                  |     | 2         |

| 38 | Dataflow-Based Design of Coarse-Grained Reconfigurable Platforms. , 2016, , .                                                                                            |     | 2         |

| 39 | Real-Time neural signal decoding on heterogeneous MPSocs based on VLIW ASIPs. Journal of Systems<br>Architecture, 2017, 76, 89-101.                                      | 4.3 | 2         |

| 40 | Dataflow Modeling for Reconfigurable Signal Processing Systems. , 2019, , 787-824.                                                                                       |     | 2         |

| 41 | Challenging CPS Trade-off Adaptivity with Coarse-Grained Reconfiguration. Lecture Notes in Electrical Engineering, 2019, , 57-63.                                        | 0.4 | 2         |

| 42 | A Network on Chip Architecture for Heterogeneous Traffic Support with Non-Exclusive Dual-Mode<br>Switching. , 2008, , .                                                  |     | 1         |

| 43 | Impact of Half-Duplex and Full-Duplex DMA Implementations on NoC Performance. , 2010, , .                                                                                |     | 1         |

| 44 | Power modelling for saving strategies in coarse grained reconfigurable systems. , 2015, , .                                                                              |     | 1         |

| 45 | Computing Swarms for Self-Adaptiveness and Self-Organization in Floating-Point Array Processing.<br>ACM Transactions on Autonomous and Adaptive Systems, 2015, 10, 1-34. | 0.8 | 1         |

| 46 | Low power design methodology for signal processing systems using lightweight dataflow techniques. , 2016, , .                                                            |     | 1         |

| 47 | Feasibility study of real-time spiking neural network simulations on a swarm intelligence based digital architecture. , 2017, , .                                        |     | 1         |

| 48 | Architecture-aware design and implementation of CNN algorithms for embedded inference: the ALOHA project. , 2018, , .                                                    |     | 1         |

| 49 | Feasibility Study and Porting of the Damped Least Square Algorithm on FPGA. IEEE Access, 2020, 8, 175483-175500.                                                         | 4.2 | 1         |

| 50 | Towards self-adaptive networks on chip for massively parallel processors. , 2011, , .                                                                                    |     | 0         |

| 51 | Demo: Reconfigurable Platform Composer Tool. , 2016, , .                                                                                                                 |     | 0         |

| 52 | Early Stage Automatic Strategy for Power-Aware Signal Processing Systems Design. Journal of Signal<br>Processing Systems, 2016, 82, 311-329.                             | 2.1 | 0         |

| 53 | Adaptive software-augmented hardware reconfiguration with dataflow design automation. , 2017, , .                                                                        |     | 0         |

| 54 | Preface to the Special Issue on Methods, Tools, and Architectures for Signal and Image Processing.<br>Journal of Signal Processing Systems, 2019, 91, 701-702.           | 2.1 | 0         |

| #  | Article                                                                                                   | IF  | CITATIONS |

|----|-----------------------------------------------------------------------------------------------------------|-----|-----------|

| 55 | Editorial: Special Issue on Computing Frontiers. Journal of Signal Processing Systems, 2019, 91, 273-273. | 2.1 | Ο         |