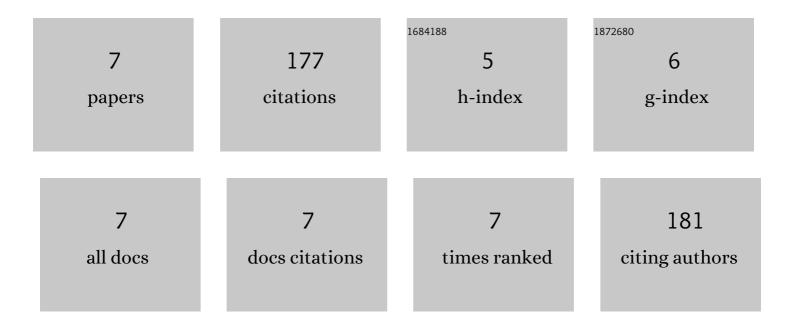

## List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/5311408/publications.pdf Version: 2024-02-01

ê 9ì2 ìz

| # | Article                                                                                                                                                                                                                | IF   | CITATIONS |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|

| 1 | A multiple negative differential resistance heterojunction device and its circuit application to ternary static random access memory. Nanoscale Horizons, 2020, 5, 654-662.                                            | 8.0  | 70        |

| 2 | Double Negative Differential Transconductance Characteristic: From Device to Circuit Application toward Quaternary Inverter. Advanced Functional Materials, 2019, 29, 1905540.                                         | 14.9 | 39        |

| 3 | A Charge-Domain Scalable-Weight In-Memory Computing Macro With Dual-SRAM Architecture for<br>Precision-Scalable DNN Accelerators. IEEE Transactions on Circuits and Systems I: Regular Papers, 2021,<br>68, 3305-3316. | 5.4  | 30        |

| 4 | A Fully Static True-Single-Phase-Clocked Dual-Edge-Triggered Flip-Flop for Near-Threshold Voltage<br>Operation in IoT Applications. IEEE Access, 2020, 8, 40232-40245.                                                 | 4.2  | 17        |

| 5 | An Ultra-Low-Power Fully-Static Contention-Free Flip-Flop With Complete Redundant Clock Transition and Transistor Elimination. IEEE Journal of Solid-State Circuits, 2021, 56, 3039-3048.                              | 5.4  | 11        |

| 6 | A Static Contention-Free Differential Flip-Flop in 28nm for Low-Voltage, Low-Power Applications. ,<br>2020, , .                                                                                                        |      | 7         |

| 7 | A Redundancy Eliminated Flip-Flop in 28 nm for Low-Voltage Low-Power Applications. IEEE Solid-State<br>Circuits Letters, 2020, 3, 446-449.                                                                             | 2.0  | 3         |