## Leibin Ni

List of Publications by Year in descending order

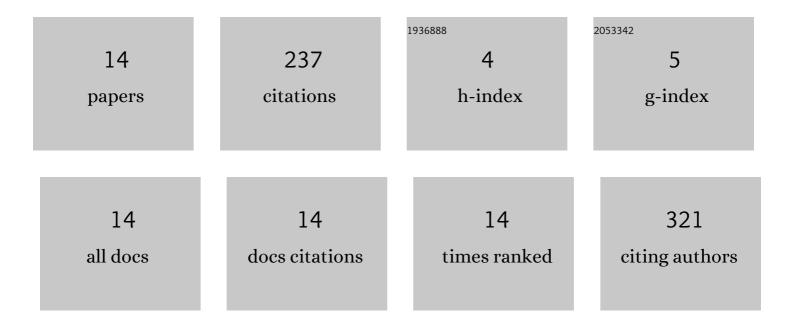

Source: https://exaly.com/author-pdf/5019545/publications.pdf Version: 2024-02-01

LEIRIN NI

| #  | Article                                                                                                                                                                                                                        | IF  | CITATIONS |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | An Energy-Efficient Nonvolatile In-Memory Computing Architecture for Extreme Learning Machine by<br>Domain-Wall Nanowire Devices. IEEE Nanotechnology Magazine, 2015, 14, 998-1012.                                            | 1.1 | 71        |

| 2  | An Energy-Efficient Digital ReRAM-Crossbar-Based CNN With Bitwise Parallelism. IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, 2017, 3, 37-46.                                                     | 1.1 | 59        |

| 3  | DW-AES: A Domain-Wall Nanowire-Based AES for High Throughput and Energy-Efficient Data<br>Encryption in Non-Volatile Memory. IEEE Transactions on Information Forensics and Security, 2016, 11,<br>2426-2440.                  | 4.5 | 40        |

| 4  | Distributed In-Memory Computing on Binary RRAM Crossbar. ACM Journal on Emerging Technologies in Computing Systems, 2017, 13, 1-18.                                                                                            | 1.8 | 35        |

| 5  | An energy-efficient matrix multiplication accelerator by distributed in-memory computing on binary RRAM crossbar. , 2016, , .                                                                                                  |     | 12        |

| 6  | On-line machine learning accelerator on digital RRAM-crossbar. , 2016, , .                                                                                                                                                     |     | 5         |

| 7  | An Energy-efficient Non-volatile In-memory Accelerator for Sparse-representation based Face Recognition. , 2015, , .                                                                                                           |     | 5         |

| 8  | LTNN: An energy-efficient machine learning accelerator on 3D CMOS-RRAM for layer-wise tensorized neural network. , 2017, , .                                                                                                   |     | 4         |

| 9  | Optimizing Boolean embedding matrix for compressive sensing in RRAM crossbar. , 2015, , .                                                                                                                                      |     | 3         |

| 10 | A Zonotoped Macromodeling for Eye-Diagram Verification of High-Speed I/O Links With Jitter and<br>Parameter Variations. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,<br>2016, 35, 1040-1051. | 1.9 | 2         |

| 11 | A Low-Power High-Throughput In-Memory CMOS-ReRAM Accelerator for Large-Scale Deep Residual<br>Neural Networks. , 2019, , .                                                                                                     |     | 1         |

| 12 | Racetrack memory-based encoder/decoder for low-power interconnect architectures. , 2016, , .                                                                                                                                   |     | 0         |

| 13 | Future brain-like computing with non-volatile memory device. , 2016, , .                                                                                                                                                       |     | 0         |

| 14 | A 3D multi-layer CMOS-RRAM accelerator for multi-layer machine learning. , 2016, , .                                                                                                                                           |     | 0         |

A 3D multi-layer CMOS-RRAM accelerator for multi-layer machine learning. , 2016, , . 14