## Baolei Mao

List of Publications by Year in descending order

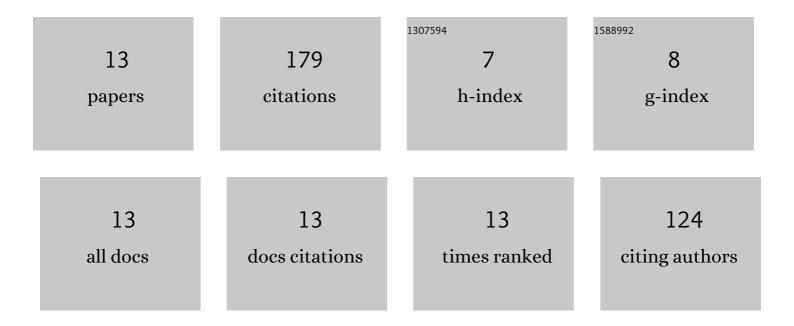

Source: https://exaly.com/author-pdf/4570206/publications.pdf Version: 2024-02-01

RADIEL MAD

| #  | Article                                                                                                                                                                                              | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | A review of hardware timing channel detection and mitigation. Journal of Physics: Conference Series, 2020, 1634, 012118.                                                                             | 0.4 | 0         |

| 2  | A formal model for proving hardware timing properties and identifying timing channels. The<br>Integration VLSI Journal, 2020, 72, 123-133.                                                           | 2.1 | 7         |

| 3  | Android Malware Detection Using Fine-Grained Features. Scientific Programming, 2020, 2020, 1-13.                                                                                                     | 0.7 | 29        |

| 4  | Theorem proof based gate level information flow tracking for hardware security verification.<br>Computers and Security, 2019, 85, 225-239.                                                           | 6.0 | 8         |

| 5  | A Simplifying Logic Approach for Gate Level Information Flow Tracking. Lecture Notes of the Institute for Computer Sciences, Social-Informatics and Telecommunications Engineering, 2018, , 302-311. | 0.3 | 0         |

| 6  | Towards Quantified Data Analysis of Information Flow Tracking for Secure System Design. IEEE Access, 2018, 6, 1822-1831.                                                                             | 4.2 | 2         |

| 7  | Quantitative Analysis of Timing Channel Security in Cryptographic Hardware Design. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2018, 37, 1719-1732.               | 2.7 | 11        |

| 8  | Leaks or Not: A Framework for Evaluating Cache Timing Side Channel Attacks in SGX. , 2018, , .                                                                                                       |     | 4         |

| 9  | Detecting Hardware Trojans with Gate-Level Information-Flow Tracking. Computer, 2016, 49, 44-52.                                                                                                     | 1.1 | 70        |

| 10 | Quantifying timing-based information flow in cryptographic hardware. , 2015, , .                                                                                                                     |     | 9         |

| 11 | Gate-Level Information Flow Tracking for Security Lattices. ACM Transactions on Design Automation of Electronic Systems, 2014, 20, 1-25.                                                             | 2.6 | 29        |

| 12 | A bottomâ€up approach to verifiable embedded system information flow security. IET Information Security, 2014, 8, 12-17.                                                                             | 1.7 | 10        |

| 13 | Secure hardware design through bit-tight information flow control. , 2013, , .                                                                                                                       |     | О         |