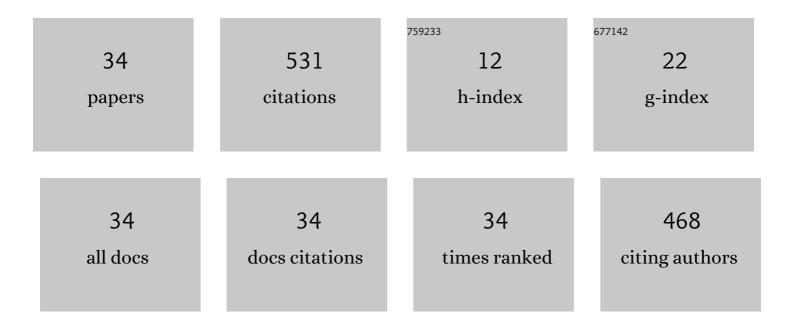

## Sebastian Hoyos

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/3684346/publications.pdf Version: 2024-02-01

| 1Recurrent Neural Network Equalization for Wireline Communication Systems. IEEE Transactions on<br>Circuits and Systems II: Express Briefs, 2022, 69, 2116-2120.3.012Special Issue on the 2022 IEEE International Symposium on Circuits and Systems. IEEE Transactions on<br>Circuits and Systems II: Express Briefs, 2022, 69, 2393-2393.3.003Multi-Channel Receiver Nonlinearity Cancellation Using Channel Speculation Passing Algorithm. IEEE<br>Transactions on Circuits and Systems II: Express Briefs, 2021, , 1-1.3.034Kalman-Based Real-Time Functional Decomposition for the Spectral Calibration in Swept Source<br>Optical Coherence Tomography. IEEE Transactions on Biomedical Circuits and Systems, 2020, 14,<br>257-273.4.025A 32 Gb/s ADC-Based PAM-4 Receiver with 2-bit/Stage SAR ADC and Partially-Unrolled DFE., 2019, , .36The Spectral Calibration of Swept-Source Optical Coherence Tomography Systems Using Unscented<br>Kalman Filter., 2018, , .27Statistical Modeling of Non-Linearity in Decision Feedback Equalizer-Based Mixed-Signal Receivers.,<br>2018, , .18Analog-to-Digital Converter-Based Serial Links: An Overview. IEEE Solid-State Circuits Magazine, 2018,<br>0, 35-47.0.4249A25 CS/s 6b T1Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS.<br>IEEE Journal of Solid-State Circuits, 2017, 52, 2168-2179.5.413 | ONS |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2       Circuits and Systems II: Express Briefs, 2022, 69, 2393-2393.       3.0       0         3       Multi-Channel Receiver Nonlinearity Cancellation Using Channel Speculation Passing Algorithm. IEEE       3.0       3         3       Multi-Channel Receiver Nonlinearity Cancellation Using Channel Speculation Passing Algorithm. IEEE       3.0       3         4       Multi-Channel Receiver Nonlinearity Cancellation Using Channel Speculation in Swept Source Optical Coherence Tomography. IEEE Transactions on Biomedical Circuits and Systems, 2020, 14, 257-273.       4.0       2         5       A 32 Cb/s ADC-Based PAM-4 Receiver with 2-bit/Stage SAR ADC and Partially-Unrolled DFE., 2019,       3       3         6       The Spectral Calibration of Swept-Source Optical Coherence Tomography Systems Using Unscented Kalman Filter., 2018,       2         7       Statistical Modeling of Non-Linearity in Decision Feedback Equalizer-Based Mixed-Signal Receivers., 2018,       1         8       Analog-to-Digital Converter-Based Serial Links: An Overview. IEEE Solid-State Circuits Magazine, 2018,       0.4       24         0       A25 CS/s 6b TI Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS.       5.4       11                                                                                           |     |

| 3       Transactions on Circuits and Systems II: Express Briefs, 2021, , 1-1.       3.0       3         4       Kalman-Based Real-Time Functional Decomposition for the Spectral Calibration in Swept Source       4.0       2         5       A 32 Cb/s ADC-Based PAM-4 Receiver with 2-bit/Stage SAR ADC and Partially-Unrolled DFE. , 2019, , .       3       3         6       The Spectral Calibration of Swept-Source Optical Coherence Tomography Systems Using Unscented Kalman Filter. , 2018, , .       2         7       Statistical Modeling of Non-Linearity in Decision Feedback Equalizer-Based Mixed-Signal Receivers. , 2018, , .       1         8       Analog-to-Digital Converter-Based Serial Links: An Overview. IEEE Solid-State Circuits Magazine, 2018, .       0.4       24         0       A25 CS/s 6b TI Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS.       5.4       12                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 4Optical Coherence Tomography. IEEE Transactions on Biomedical Circuits and Systems, 2020, 14,<br>257-273.4.025A 32 Gb/s ADC-Based PAM-4 Receiver with 2-bit/Stage SAR ADC and Partially-Unrolled DFE., 2019, , .36The Spectral Calibration of Swept-Source Optical Coherence Tomography Systems Using Unscented<br>Kalman Filter., 2018, , .27Statistical Modeling of Non-Linearity in Decision Feedback Equalizer-Based Mixed-Signal Receivers. ,<br>2018, , .18Analog-to-Digital Converter-Based Serial Links: An Overview. IEEE Solid-State Circuits Magazine, 2018,<br>10, 35-47.0.4240A 25 GS/s 6b TI Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS.5.413                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| <ul> <li>The Spectral Calibration of Swept-Source Optical Coherence Tomography Systems Using Unscented Kalman Filter., 2018, ,.</li> <li>Statistical Modeling of Non-Linearity in Decision Feedback Equalizer-Based Mixed-Signal Receivers., 2018, ,.</li> <li>Analog-to-Digital Converter-Based Serial Links: An Overview. IEEE Solid-State Circuits Magazine, 2018, 0.4 24</li> <li>A 25 CS/s 6b TI Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS. 54 12</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _   |

| <ul> <li>Kalman Filter., 2018, ,</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| <ul> <li>Analog-to-Digital Converter-Based Serial Links: An Overview. IEEE Solid-State Circuits Magazine, 2018, 0.4 24</li> <li>A 25 GS/s 6b TI Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS. 5.4 18</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| A 25 GS/s 6b TI Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 10Compressed Level Crossing Sampling for Ultra-Low Power IoT Devices. IEEE Transactions on Circuits<br>and Systems I: Regular Papers, 2017, 64, 2495-2507.5.49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 11 Towards an on-chip signal processing solution for the online calibration of SS-OCT systems. , 2017, , . 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| A 10 Gb/s Hybrid ADC-Based Receiver With Embedded Analog and Per-Symbol Dynamically Enabled Digital<br>Equalization. IEEE Journal of Solid-State Circuits, 2016, 51, 671-685. 5.4 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| A Process-Variation Resilient Current Mode Logic With Simultaneous Regulations for Time Constant,<br>13 Voltage Swing, Level Shifting, and DC Gain Using Time-Reference-Based Adaptive Biasing Chain. IEEE 3.1 1<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23, 198-202.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 14Towards a Standard Mixed-Signal Parallel Processing Architecture for Miniature and Microrobotics.1.2114Journal of Research of the National Institute of Standards and Technology, 2014, 119, 529.1.21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 15 Statistical modeling of metastability in ADC-based serial I/O receivers. , 2014, , . 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| A single parity check forward error correction method for high speed I/O., 2014, , . 2014, 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| A 6 bit 10 GS/s TI-SAR ADC With Low-Overhead Embedded FFE/DFE Equalization for Wireline Receiver 5.4 20<br>Applications. IEEE Journal of Solid-State Circuits, 2014, 49, 2560-2574.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

Asynchronous Binary Compressive Sensing for Wireless Body Sensor Networks. , 2013, , .

1

SEBASTIAN HOYOS

| #  | Article                                                                                                                                                                                                                            | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | A 6-b 1.6-GS/s ADC With Redundant Cycle One-Tap Embedded DFE in 90-nm CMOS. IEEE Journal of Solid-State Circuits, 2013, 48, 1885-1897.                                                                                             | 5.4 | 14        |

| 20 | LEAST MEAN SQUARED BACKGROUND CALIBRATION FOR OFDM MULTICHANNEL RECEIVERS. Journal of Circuits, Systems and Computers, 2012, 21, 1250014.                                                                                          | 1.5 | 1         |

| 21 | Digital-Assisted Asynchronous Compressive Sensing Front-End. IEEE Journal on Emerging and Selected<br>Topics in Circuits and Systems, 2012, 2, 482-492.                                                                            | 3.6 | 12        |

| 22 | Sensitivity Analysis of Continuous-Time \$Delta Sigma\$ ADCs to Out-of-Band Blockers in Future<br>SAW-Less Multi-Standard Wireless Receivers. IEEE Transactions on Circuits and Systems I: Regular<br>Papers, 2012, 59, 1894-1905. | 5.4 | 12        |

| 23 | The impact of ADC nonlinearity in a mixed-signal compressive sensing system for frequency-domain sparse signals. Physical Communication, 2012, 5, 196-207.                                                                         | 2.1 | 11        |

| 24 | Clock-Jitter-Tolerant Wideband Receivers: An Optimized Multichannel Filter-Bank Approach. IEEE<br>Transactions on Circuits and Systems I: Regular Papers, 2011, 58, 253-263.                                                       | 5.4 | 16        |

| 25 | A 2.8-mW Sub-2-dB Noise-Figure Inductorless Wideband CMOS LNA Employing Multiple Feedback. IEEE<br>Transactions on Microwave Theory and Techniques, 2011, 59, 3154-3161.                                                           | 4.6 | 85        |

| 26 | Sensitivity analysis of pulse-width jitter induced noise in continuous-time delta-sigma modulators to out-of-band blockers in wireless receivers. , 2011, , .                                                                      |     | 3         |

| 27 | Wideband Common-Gate CMOS LNA Employing Dual Negative Feedback With Simultaneous Noise, Gain, and Bandwidth Optimization. IEEE Transactions on Microwave Theory and Techniques, 2010, 58, 2340-2351.                               | 4.6 | 118       |

| 28 | A Sixth-Order 200 MHz IF Bandpass Sigma-Delta Modulator With Over 68 dB SNDR in 10 MHz Bandwidth.<br>IEEE Journal of Solid-State Circuits, 2010, 45, 1122-1136.                                                                    | 5.4 | 61        |

| 29 | A Multiphase Multipath Technique With Digital Phase Shifters for Harmonic Distortion Cancellation.<br>IEEE Transactions on Circuits and Systems II: Express Briefs, 2010, 57, 921-925.                                             | 3.0 | 12        |

| 30 | A 1.8V, sub-mW, over 100% locking range, divide-by-3 and 7 complementary-injection-locked 4 GHz frequency divider. , 2009, , .                                                                                                     |     | 11        |

| 31 | A CMOS differential noise cancelling low noise transconductance amplifier. , 2008, , .                                                                                                                                             |     | 8         |

| 32 | Applications of Multipath Transform-Domain Charge-Sampling Wide-Band Receivers. IEEE Transactions on Circuits and Systems II: Express Briefs, 2008, 55, 309-313.                                                                   | 3.0 | 17        |

| 33 | Compressed UWB signal detection with narrowband interference mitigation. , 2008, , .                                                                                                                                               |     | 21        |

| 34 | UWB Mixed-Signal Transform-Domain Direct-Sequence Receiver. IEEE Transactions on Wireless<br>Communications, 2007, 6, 3038-3046.                                                                                                   | 9.2 | 19        |