List of Publications by Year in descending order

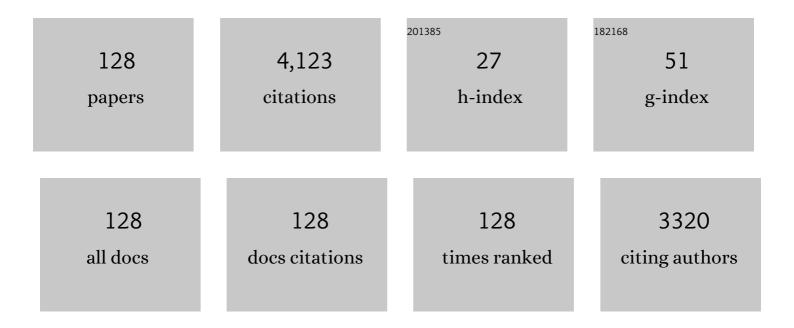

Source: https://exaly.com/author-pdf/3132337/publications.pdf Version: 2024-02-01

Νισλικίηλ

| #  | Article                                                                                                                                                                                           | IF   | CITATIONS |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|

| 1  | GARNET: A detailed on-chip network model inside a full-system simulator. , 2009, , .                                                                                                              |      | 522       |

| 2  | A Comprehensive Study of Security of Internet-of-Things. IEEE Transactions on Emerging Topics in Computing, 2017, 5, 586-602.                                                                     | 3.2  | 464       |

| 3  | MedMon: Securing Medical Devices Through Wireless Monitoring and Anomaly Detection. IEEE Transactions on Biomedical Circuits and Systems, 2013, 7, 871-881.                                       | 2.7  | 174       |

| 4  | ChamNet: Towards Efficient Network Design Through Platform-Aware Model Adaptation. , 2019, , .                                                                                                    |      | 146       |

| 5  | FinFETs: From Devices to Architectures. Advances in Electronics, 2014, 2014, 1-21.                                                                                                                | 1.9  | 137       |

| 6  | System-Level Dynamic Thermal Management for High-Performance Microprocessors. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27, 96-108.                    | 1.9  | 131       |

| 7  | NeST: A Neural Network Synthesis Tool Based on a Grow-and-Prune Paradigm. IEEE Transactions on Computers, 2019, 68, 1487-1497.                                                                    | 2.4  | 108       |

| 8  | Wearable Medical Sensor-Based System Design: A Survey. IEEE Transactions on Multi-Scale Computing Systems, 2017, 3, 124-138.                                                                      | 2.5  | 104       |

| 9  | Keep the Stress Away with SoDA: Stress Detection and Alleviation System. IEEE Transactions on Multi-Scale Computing Systems, 2017, 3, 269-282.                                                    | 2.5  | 97        |

| 10 | Trustworthiness of Medical Devices and Body Area Networks. Proceedings of the IEEE, 2014, 102, 1174-1188.                                                                                         | 16.4 | 95        |

| 11 | CMOS logic design with independent-gate FinFETs. , 2007, , .                                                                                                                                      |      | 88        |

| 12 | A Health Decision Support System for Disease Diagnosis Based on Wearable Medical Sensors and<br>Machine Learning Ensembles. IEEE Transactions on Multi-Scale Computing Systems, 2017, 3, 228-241. | 2.5  | 84        |

| 13 | Energy-Efficient Long-term Continuous Personal Health Monitoring. IEEE Transactions on Multi-Scale<br>Computing Systems, 2015, 1, 85-98.                                                          | 2.5  | 78        |

| 14 | Token flow control. , 2008, , .                                                                                                                                                                   |      | 73        |

| 15 | Hardware-Assisted Run-Time Monitoring for Secure Program Execution on Embedded Processors. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2006, 14, 1295-1308.              | 2.1  | 66        |

| 16 | Design of Logic Gates and Flip-Flops in High-Performance FinFET Technology. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2013, 21, 1975-1988.                             | 2.1  | 57        |

| 17 | 3-D-TCAD-Based Parasitic Capacitance Extraction for Emerging Multigate Devices and Circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2013, 21, 2094-2105.               | 2.1  | 49        |

| 18 | CABA: Continuous Authentication Based on BioAura. IEEE Transactions on Computers, 2017, 66, 759-772.                                                                                              | 2.4  | 48        |

| #  | Article                                                                                                                                                                                                                                  | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | A Test Generation Framework for Quantum Cellular Automata Circuits. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2007, 15, 24-36.                                                                                | 2.1 | 47        |

| 20 | PAQCS: Physical Design-Aware Fault-Tolerant Quantum Circuit Synthesis. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2015, 23, 1221-1234.                                                                         | 2.1 | 47        |

| 21 | Majority and Minority Network Synthesis With Application to QCA-, SET-, and TPL-Based<br>Nanotechnologies. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,<br>2007, 26, 1233-1245.                        | 1.9 | 46        |

| 22 | Power-Efficient Scheduling for Heterogeneous Distributed Real-Time Embedded Systems. IEEE<br>Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26, 1161-1170.                                              | 1.9 | 46        |

| 23 | In-Network Snoop Ordering (INSO): Snoopy coherence on unordered interconnects. , 2009, , .                                                                                                                                               |     | 45        |

| 24 | A Trusted Virtual Machine in an Untrusted Management Environment. IEEE Transactions on Services<br>Computing, 2012, 5, 472-483.                                                                                                          | 3.2 | 45        |

| 25 | Grow and Prune Compact, Fast, and Accurate LSTMs. IEEE Transactions on Computers, 2020, 69, 441-452.                                                                                                                                     | 2.4 | 44        |

| 26 | Simultaneous Dynamic Voltage Scaling of Processors and Communication Links in Real-Time<br>Distributed Embedded Systems. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2007,<br>15, 427-437.                         | 2.1 | 40        |

| 27 | Smart, Secure, Yet Energy-Efficient, Internet-of-Things Sensors. IEEE Transactions on Multi-Scale<br>Computing Systems, 2018, 4, 914-930.                                                                                                | 2.5 | 40        |

| 28 | CovidDeep: SARS-CoV-2/COVID-19 Test Based on Wearable Medical Sensors and Efficient Neural Networks. IEEE Transactions on Consumer Electronics, 2021, 67, 244-256.                                                                       | 3.0 | 39        |

| 29 | SLOPES: Hardware–Software Cosynthesis of Low-Power Real-Time Distributed Embedded Systems With<br>Dynamically Reconfigurable FPGAs. IEEE Transactions on Computer-Aided Design of Integrated Circuits<br>and Systems, 2007, 26, 508-526. | 1.9 | 36        |

| 30 | Vibration-based secure side channel for medical devices. , 2015, , .                                                                                                                                                                     |     | 35        |

| 31 | Signal Processing With Direct Computations on Compressively Sensed Data. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2015, 23, 30-43.                                                                           | 2.1 | 34        |

| 32 | Improving the Trustworthiness of Medical Device Software with Formal Verification Methods. IEEE<br>Embedded Systems Letters, 2013, 5, 50-53.                                                                                             | 1.3 | 33        |

| 33 | Fault modeling for FinFET circuits. , 2010, , .                                                                                                                                                                                          |     | 30        |

| 34 | Physiological Information Leakage: A New Frontier in Health Information Security. IEEE Transactions on Emerging Topics in Computing, 2016, 4, 321-334.                                                                                   | 3.2 | 30        |

| 35 | A Scalable Synthesis Methodology for Application-Specific Processors. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2006, 14, 1175-1188.                                                                          | 2.1 | 28        |

| 36 | Generation of Heterogeneous Distributed Architectures for Memory-Intensive Applications Through<br>High-Level Synthesis. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2007, 15,<br>1191-1204.                       | 2.1 | 27        |

| #  | Article                                                                                                                                                                                                               | IF  | CITATIONS |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 37 | Fault Models for Logic Circuits in the Multigate Era. IEEE Nanotechnology Magazine, 2012, 11, 182-193.                                                                                                                | 1.1 | 26        |

| 38 | FinPrin: FinFET Logic Circuit Analysis and Optimization Under PVT Variations. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22, 2462-2475.                                                  | 2.1 | 25        |

| 39 | PinMe: Tracking a Smartphone User around the World. IEEE Transactions on Multi-Scale Computing Systems, 2018, 4, 420-435.                                                                                             | 2.5 | 25        |

| 40 | Smart Healthcare. Foundations and Trends in Electronic Design Automation, 2018, 12, 401-166.                                                                                                                          | 1.0 | 25        |

| 41 | Emerging Frontiers in Embedded Security. , 2013, , .                                                                                                                                                                  |     | 24        |

| 42 | FTQLS: Fault-Tolerant Quantum Logic Synthesis. IEEE Transactions on Very Large Scale Integration<br>(VLSI) Systems, 2014, 22, 1350-1363.                                                                              | 2.1 | 23        |

| 43 | A Synthesis Methodology for Hybrid Custom Instruction and Coprocessor Generation for Extensible<br>Processors. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26,<br>2035-2045. | 1.9 | 22        |

| 44 | Design of ultra-low-leakage logic gates and flip-flops in high-performance FinFET technology. , 2011, , .                                                                                                             |     | 22        |

| 45 | Die-level leakage power analysis of FinFET circuits considering process variations. , 2010, , .                                                                                                                       |     | 21        |

| 46 | FinCANON: A PVT-Aware Integrated Delay and Power Modeling Framework for FinFET-Based Caches and<br>On-Chip Networks. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22, 1150-1163.           | 2.1 | 21        |

| 47 | Satisfiability-Based Automatic Test Program Generation and Design for Testability for<br>Microprocessors. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2007, 15, 518-530.                        | 2.1 | 19        |

| 48 | Optimized Quantum Gate Library for Various Physical Machine Descriptions. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2013, 21, 2055-2068.                                                   | 2.1 | 18        |

| 49 | Energy-efficient and Secure Sensor Data Transmission Using Encompression. , 2013, , .                                                                                                                                 |     | 18        |

| 50 | A Fine-Grain Dynamically Reconfigurable Architecture Aimed at Reducing the FPGA-ASIC Gaps. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22, 2607-2620.                                  | 2.1 | 18        |

| 51 | Low-power FinFET circuit synthesis using surface orientation optimization. , 2010, , .                                                                                                                                |     | 17        |

| 52 | A Hierarchical Inference Model for Internet-of-Things. IEEE Transactions on Multi-Scale Computing<br>Systems, 2018, 4, 260-271.                                                                                       | 2.5 | 17        |

| 53 | DiabDeep: Pervasive Diabetes Diagnosis Based on Wearable Medical Sensors and Efficient Neural<br>Networks. IEEE Transactions on Emerging Topics in Computing, 2021, 9, 1139-1150.                                     | 3.2 | 17        |

| 54 | Hybrid Simulation for Energy Estimation of Embedded Software. IEEE Transactions on Computer-Aided<br>Design of Integrated Circuits and Systems, 2007, 26, 1843-1854.                                                  | 1.9 | 16        |

| #  | Article                                                                                                                                                                                                                    | IF  | CITATIONS |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 55 | Architectural Support for Run-Time Validation of Program Data Properties. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2007, 15, 546-559.                                                          | 2.1 | 16        |

| 56 | Design of Efficient Content Addressable Memories in High-Performance FinFET Technology. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23, 963-967.                                            | 2.1 | 16        |

| 57 | Automated Energy/Performance Macromodeling of Embedded Software. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26, 542-552.                                                         | 1.9 | 15        |

| 58 | Aiding Side-Channel Attacks on Cryptographic Software With Satisfiability-Based Analysis. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2007, 15, 465-470.                                          | 2.1 | 15        |

| 59 | Efficient Methodologies for 3-D TCAD Modeling of Emerging Devices and Circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2013, 32, 47-58.                                            | 1.9 | 15        |

| 60 | Incremental Learning Using a Grow-and-Prune Paradigm With Efficient Neural Networks. IEEE<br>Transactions on Emerging Topics in Computing, 2022, 10, 752-762.                                                              | 3.2 | 15        |

| 61 | Energy-Efficient Monolithic Three-Dimensional On-Chip Memory Architectures. IEEE Nanotechnology<br>Magazine, 2018, 17, 620-633.                                                                                            | 1.1 | 15        |

| 62 | An evaluation of energy-saving technologies for residential purposes. , 2010, , .                                                                                                                                          |     | 14        |

| 63 | SRAM-Based NATURE: A Dynamically Reconfigurable FPGA Based on 10T Low-Power SRAMs. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2012, 20, 2151-2156.                                               | 2.1 | 14        |

| 64 | Ultra-High Density Monolithic 3-D FinFET SRAM With Enhanced Read Stability. IEEE Transactions on<br>Circuits and Systems I: Regular Papers, 2016, 63, 1176-1187.                                                           | 3.5 | 14        |

| 65 | MHDeep: Mental Health Disorder Detection System Based on Wearable Sensors and Artificial Neural Networks. Transactions on Embedded Computing Systems, 2022, 21, 1-22.                                                      | 2.1 | 14        |

| 66 | Automatic Test Generation for Combinational Threshold Logic Networks. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2008, 16, 1035-1045.                                                            | 2.1 | 13        |

| 67 | FinFET-based dynamic power management of on-chip interconnection networks through adaptive back-gate biasing. , 2009, , .                                                                                                  |     | 13        |

| 68 | GenFin: Genetic Algorithm-Based Multiobjective Statistical Logic Circuit Optimization Using<br>Incremental Statistical Analysis. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016,<br>24, 1126-1139. | 2.1 | 13        |

| 69 | Three-Dimensional Monolithic FinFET-Based 8T SRAM Cell Design for Enhanced Read Time and Low<br>Leakage. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019, 27, 899-912.                              | 2.1 | 13        |

| 70 | Fully Dynamic Inference with Deep Neural Networks. IEEE Transactions on Emerging Topics in Computing, 2021, , 1-1.                                                                                                         | 3.2 | 13        |

| 71 | Threshold Voltage Control through Multiple Supply Voltages for Power-Efficient FinFET<br>Interconnects. , 2008, , .                                                                                                        |     | 12        |

| 72 | SPRING: A Sparsity-Aware Reduced-Precision Monolithic 3D CNN Accelerator Architecture for Training and Inference. IEEE Transactions on Emerging Topics in Computing, 2022, 10, 237-249.                                    | 3.2 | 12        |

| #  | Article                                                                                                                                                                                                          | IF  | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 73 | Software-Defined Design Space Exploration for an Efficient DNN Accelerator Architecture. IEEE<br>Transactions on Computers, 2021, 70, 45-56.                                                                     | 2.4 | 12        |

| 74 | SCANN: Synthesis of Compact and Accurate Neural Networks. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41, 3012-3025.                                                    | 1.9 | 12        |

| 75 | Low-power 3D nano/CMOS hybrid dynamically reconfigurable architecture. ACM Journal on Emerging<br>Technologies in Computing Systems, 2010, 6, 1-32.                                                              | 1.8 | 11        |

| 76 | Algorithm-Driven Architectural Design Space Exploration of Domain-Specific Medical-Sensor<br>Processors. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2013, 21, 1849-1862.                  | 2.1 | 11        |

| 77 | A 3-D CPU-FPGA-DRAM Hybrid Architecture for Low-Power Computation. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24, 1649-1662.                                                        | 2.1 | 11        |

| 78 | McPAT-Monolithic: An Area/Power/Timing Architecture Modeling Framework for 3-D Hybrid<br>Monolithic Multicore Systems. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020,<br>28, 2146-2156. | 2.1 | 11        |

| 79 | A defense framework against malware and vulnerability exploits. International Journal of Information Security, 2014, 13, 439-452.                                                                                | 2.3 | 10        |

| 80 | SHARKS: Smart Hacking Approaches for RisK Scanning in Internet-of-Things and Cyber-Physical Systems based on Machine learning. IEEE Transactions on Emerging Topics in Computing, 2021, , 1-1.                   | 3.2 | 10        |

| 81 | Machine Learning Assisted Security Analysis of 5G-Network-Connected Systems. IEEE Transactions on Emerging Topics in Computing, 2022, 10, 2006-2024.                                                             | 3.2 | 10        |

| 82 | DISASTER: Dedicated Intelligent Security Attacks on Sensor-Triggered Emergency Responses. IEEE<br>Transactions on Multi-Scale Computing Systems, 2017, 3, 255-268.                                               | 2.5 | 9         |

| 83 | Genetic Programming for Energy-Efficient and Energy-Scalable Approximate Feature Computation in Embedded Inference Systems. IEEE Transactions on Computers, 2018, 67, 222-236.                                   | 2.4 | 9         |

| 84 | A Monolithic 3D Hybrid Architecture for Energy-Efficient Computation. IEEE Transactions on<br>Multi-Scale Computing Systems, 2018, 4, 533-547.                                                                   | 2.5 | 9         |

| 85 | Simultaneously ensuring smartness, security, and energy efficiency in Internet-of-Things sensors. , 2018, , .                                                                                                    |     | 9         |

| 86 | Variable-Pipeline-Stage Router. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2013, 21, 1669-1682.                                                                                           | 2.1 | 8         |

| 87 | Making buildings energy-efficient through retrofits: A survey of available technologies. , 2013, , .                                                                                                             |     | 8         |

| 88 | Hybrid Monolithic 3-D IC Floorplanner. IEEE Transactions on Very Large Scale Integration (VLSI)<br>Systems, 2018, 26, 1868-1880.                                                                                 | 2.1 | 8         |

| 89 | Hybrid Architectures for Efficient and Secure Face Authentication in Embedded Systems. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2007, 15, 296-308.                                   | 2.1 | 7         |

| 90 | Configuration and Extension of Embedded Processors to Optimize IPSec Protocol Execution. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2007, 15, 605-609.                                 | 2.1 | 7         |

| #   | Article                                                                                                                                                                                                                                   | lF  | CITATIONS |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 91  | Pragmatic design of gated-diode FinFET DRAMs. , 2009, , .                                                                                                                                                                                 |     | 7         |

| 92  | FDR 2.0: A Low-Power Dynamically Reconfigurable Architecture and Its FinFET Implementation. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23, 1987-2000.                                                        | 2.1 | 7         |

| 93  | Convolutional Autoencoder-Based Transfer Learning for Multi-Task Image Inferences. IEEE<br>Transactions on Emerging Topics in Computing, 2021, , 1-1.                                                                                     | 3.2 | 7         |

| 94  | A system-level perspective for efficient NoC design. Parallel and Distributed Processing Symposium (IPDPS), Proceedings of the International Conference on, 2008, , .                                                                     | 1.0 | 6         |

| 95  | Low-Power FinFET design schemes for NOR address decoders. , 2010, , .                                                                                                                                                                     |     | 6         |

| 96  | FinFET Logic Circuit Optimization with Different FinFET Styles: Lower Power Possible at Higher Supply<br>Voltage. , 2014, , .                                                                                                             |     | 6         |

| 97  | OpSecure: A Secure Unidirectional Optical Channel for Implantable Medical Devices. IEEE Transactions on Multi-Scale Computing Systems, 2018, 4, 410-419.                                                                                  | 2.5 | 6         |

| 98  | Improving Convergence and Simulation Time of Quantum Hydrodynamic Simulation: Application to<br>Extraction of Best 10-nm FinFET Parameter Values. IEEE Transactions on Very Large Scale Integration<br>(VLSI) Systems, 2017, 25, 319-329. | 2.1 | 5         |

| 99  | Automated Quantum Circuit Synthesis and Cost Estimation for the Binary Welded Tree Oracle. ACM<br>Journal on Emerging Technologies in Computing Systems, 2017, 13, 1-14.                                                                  | 1.8 | 5         |

| 100 | Smart healthcare. , 2018, , .                                                                                                                                                                                                             |     | 5         |

| 101 | GRAVITAS: Graphical Reticulated Attack Vectors for Internet-of-Things Aggregate Security. IEEE Transactions on Emerging Topics in Computing, 2022, 10, 1331-1348.                                                                         | 3.2 | 5         |

| 102 | Design of Algorithm-Based Fault Tolerant Systems with In-System Checks. , 1993, , .                                                                                                                                                       |     | 4         |

| 103 | Evaluation of multiple supply and threshold voltages for low-power FinFET circuit synthesis. , 2008, , .                                                                                                                                  |     | 4         |

| 104 | Variability-Tolerant Register-Transfer Level Synthesis. , 2008, , .                                                                                                                                                                       |     | 4         |

| 105 | Design of Quantum Circuits for Random Walk Algorithms. , 2012, , .                                                                                                                                                                        |     | 4         |

| 106 | YSUY: Your Smartphone Understands You—Using Machine Learning to Address Fundamental Human<br>Needs. IEEE Transactions on Systems, Man, and Cybernetics: Systems, 2021, 51, 7553-7568.                                                     | 5.9 | 4         |

| 107 | Localized Heating for Building Energy Efficiency. , 2013, , .                                                                                                                                                                             |     | 3         |

| 108 | TCAD-Assisted Capacitance Extraction of FinFET SRAM and Logic Arrays. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2016, 24, 329-333.                                                                             | 2.1 | 3         |

| #   | Article                                                                                                                                                                                                          | IF  | CITATIONS |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 109 | A heterogeneous microprocessor for energy-scalable sensor inference using genetic programming. , 2017, , .                                                                                                       |     | 3         |

| 110 | Analytical Modeling of the SMART NoC. IEEE Transactions on Multi-Scale Computing Systems, 2017, 3, 242-254.                                                                                                      | 2.5 | 3         |

| 111 | Fast Design Space Exploration of Nonlinear Systems: Part II. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41, 2984-2999.                                                 | 1.9 | 3         |

| 112 | Efficient Design for Testability Solution Based on Unsatisfiability for Register-Transfer Level Circuits.<br>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26, 1339-1345. | 1.9 | 2         |

| 113 | Fin Prin: Analysis and Optimization of FinFET Logic Circuits under PVT Variations. , 2013, , .                                                                                                                   |     | 2         |

| 114 | CURIOUS: Efficient Neural Architecture Search Based on a Performance Predictor and Evolutionary Search. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, 41, 4975-4990.      | 1.9 | 2         |

| 115 | Fast Enhancement of Validation Test Sets for Improving the Stuck-at Fault Coverage of RTL Circuits.<br>IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2009, 17, 697-708.                      | 2.1 | 1         |

| 116 | Thermal characterization of BIST, scan design and sequential test methodologies. , 2009, , .                                                                                                                     |     | 1         |

| 117 | TCAD structure synthesis and capacitance extraction of a voltage-controlled oscillator using automated layout-to-device synthesis methodology. , 2014, , .                                                       |     | 1         |

| 118 | Using a Device State Library to Boost the Performance of TCAD Mixed-Mode Simulation. IEEE<br>Transactions on Very Large Scale Integration (VLSI) Systems, 2017, 25, 2616-2624.                                   | 2.1 | 1         |

| 119 | SECRET: Semantically Enhanced Classification of Real-World Tasks. IEEE Transactions on Computers, 2021, 70, 440-456.                                                                                             | 2.4 | 1         |

| 120 | TUTOR: Training Neural Networks Using Decision Rules as Model Priors. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2023, 42, 483-496.                                          | 1.9 | 1         |

| 121 | Simultaneous dynamic voltage scaling of processors and communication links in real-time distributed embedded systems. , 0, , .                                                                                   |     | 0         |

| 122 | What is majority/minority network synthesis?. ACM SIGDA Newsletter, 2008, 38, 1-1.                                                                                                                               | 0.0 | 0         |

| 123 | What is majority/minority network synthesis?. ACM SIGDA Newsletter, 2008, 38, 1-1.                                                                                                                               | 0.0 | 0         |

| 124 | Editorial Appointments for the 2009-2010 Term. IEEE Transactions on Very Large Scale Integration (VLSI)<br>Systems, 2009, 17, 453-469.                                                                           | 2.1 | 0         |

| 125 | Editorial : New Associate Editor Appointments. IEEE Transactions on Very Large Scale Integration (VLSI)<br>Systems, 2010, 18, 345-346.                                                                           | 2.1 | 0         |

| 126 | NanoV: Nanowire-based VLSI design. , 2010, , .                                                                                                                                                                   |     | 0         |

| #   | Article                                                                                                                                        | IF  | CITATIONS |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 127 | Editorial - Announcing a New Editor-in-Chief. IEEE Transactions on Very Large Scale Integration (VLSI)<br>Systems, 2011, 19, 173-174.          | 2.1 | 0         |

| 128 | Towards Execution-Efficient LSTMs via Hardware-Guided Grow-and-Prune Paradigm. IEEE Transactions on Emerging Topics in Computing, 2021, , 1-1. | 3.2 | 0         |