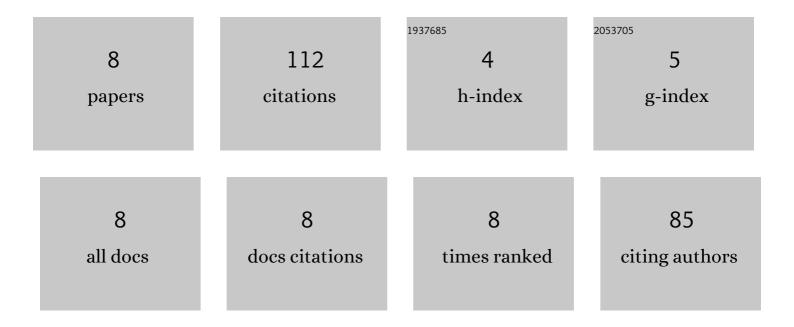

## Zhixuan Wang

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/2895050/publications.pdf

Version: 2024-02-01

| # | Article                                                                                                                                                                                                                                      | IF  | CITATIONS |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1 | A 148-nW Reconfigurable Event-Driven Intelligent Wake-Up System for AloT Nodes Using an<br>Asynchronous Pulse-Based Feature Extractor and a Convolutional Neural Network. IEEE Journal of<br>Solid-State Circuits, 2021, 56, 3274-3288.      | 5.4 | 18        |

| 2 | Ultra-Low-Power and Performance-Improved Logic Circuit Using Hybrid TFET-MOSFET Standard Cells<br>Topologies and Optimized Digital Front-End Process. IEEE Transactions on Circuits and Systems I:<br>Regular Papers, 2021, 68, 1160-1170.   | 5.4 | 12        |

| 3 | Re-Assessment of Steep-Slope Device Design From a Circuit-Level Perspective Using Novel Evaluation<br>Criteria and Model-Less Method. IEEE Transactions on Circuits and Systems I: Regular Papers, 2021, 68,<br>1624-1635.                   | 5.4 | 1         |

| 4 | A Software-Defined Always-On System With 57–75-nW Wake-Up Function Using Asynchronous<br>Clock-Free Pipelined Event-Driven Architecture and Time-Shielding Level-Crossing ADC. IEEE Journal of<br>Solid-State Circuits, 2021, 56, 2804-2816. | 5.4 | 12        |

| 5 | The Challenges and Emerging Technologies for Low-Power Artificial Intelligence IoT Systems. IEEE<br>Transactions on Circuits and Systems I: Regular Papers, 2021, 68, 4821-4834.                                                             | 5.4 | 24        |

| 6 | 20.2 A 57nW Software-Defined Always-On Wake-Up Chip for IoT Devices with Asynchronous Pipelined Event-Driven Architecture and Time-Shielding Level-Crossing ADC. , 2020, , .                                                                 |     | 24        |

| 7 | Ultra-Low Power Hybrid TFET-MOSFET Topologies for Standard Logic Cells with Improved Comprehensive Performance. , 2019, , .                                                                                                                  |     | 11        |

| 8 | Combinational Access Tunnel FET SRAM for Ultra-Low Power Applications. , 2018, , .                                                                                                                                                           |     | 10        |