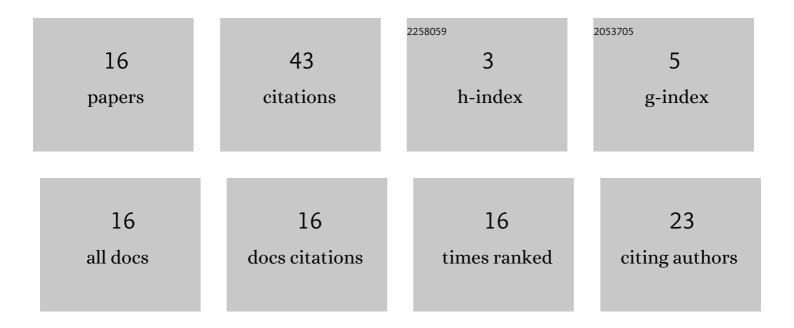

## Ganapathi Hegde

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/2740510/publications.pdf Version: 2024-02-01

CANADATHI HECDE

| #  | Article                                                                                                                                                                               | IF  | CITATIONS |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | An efficient hardware model for RSA Encryption system using Vedic mathematics. Procedia<br>Engineering, 2012, 30, 124-128.                                                            | 1.2 | 16        |

| 2  | High performance VLSI architecture for 3-D DWT (discrete Wavelet Transform). , 2018, , .                                                                                              |     | 5         |

| 3  | Systolic array based motion estimation architecture of 3D DWT sub band component for video processing. International Journal of Signal and Imaging Systems Engineering, 2012, 5, 158. | 0.6 | 3         |

| 4  | A parallel 3-D discrete wavelet transform architecture using pipelined lifting scheme approach for video coding. International Journal of Electronics, 2013, 100, 1429-1440.          | 1.4 | 3         |

| 5  | VLSI implementation of the video encoder using an efficient 3-D DCT algorithm. International Journal of Electronics Letters, 2016, 4, 38-49.                                          | 1.2 | 3         |

| 6  | Improving the Reliability of Embedded Memories using ECC and Built-In Self-Repair Techniques. , 2018, , .                                                                             |     | 3         |

| 7  | An Efficient Distributive Arithmetic Based 3-Dimensional Discrete Wavelet Transform for Video Processing. , 2011, , .                                                                 |     | 2         |

| 8  | High performance VLSI architecture for 2-D DWT using lifting scheme. , 2015, , .                                                                                                      |     | 2         |

| 9  | FPGA Implementation of 8-bit SSA Multiplier for designing OFDM Transceiver. , 2019, , .                                                                                               |     | 2         |

| 10 | An efficient 3-dimensional discrete wavelet transform architecture for video processing application.<br>Journal of Electronics, 2012, 29, 534-540.                                    | 0.2 | 1         |

| 11 | An approach for area and power optimization of flipping 3-D discrete wavelet transform architecture. , 2017, , .                                                                      |     | 1         |

| 12 | An efficient hardware realization of diamond search algorithm for motion estimation task in video compression applications. , 2017, , .                                               |     | 1         |

| 13 | An efficient hybrid integer coefficient-DCT architecture using quantization module for HEVC standard. , 2017, , .                                                                     |     | 1         |

| 14 | A Novel Low Voltage Hybrid Phase Locked Loop. , 2017, , .                                                                                                                             |     | 0         |

| 15 | High Throughput Pipelined S-Boxes for Encryption and Watermarking Applications. , 2020, , .                                                                                           |     | Ο         |

| 16 | Conservative Approximation–Based Full-Search Block Matching Algorithm Architecture for QCIF<br>Digital Video Employing Systolic Array Architecture. ETRI Journal, 2015, 37, 772-779.  | 2.0 | 0         |