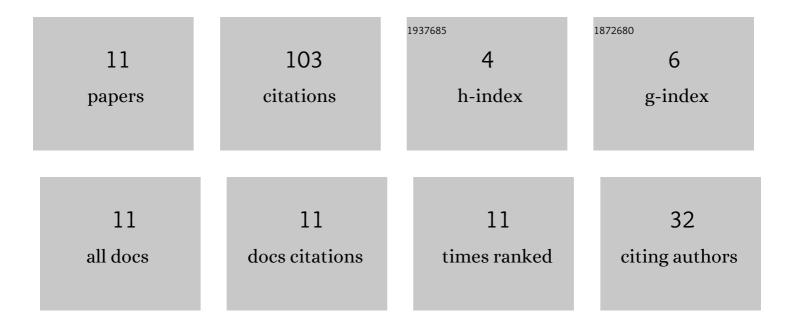

## Avaneesh K Dubey

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/1676663/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                                                                                       | IF  | CITATIONS |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | Design and Performance of High-Speed Energy-Efficient CMOS Double Tail Dynamic Latch Comparator<br>Using GACOBA Load Suitable for Low Voltage Applications. Journal of Circuits, Systems and<br>Computers, 2021, 30, 2150191. | 1.5 | 2         |

| 2  | Design and Performance of High-Speed CMOS Double-Tail Dynamic Comparator Suitable for Mixed-Signal ICs. Lecture Notes in Electrical Engineering, 2021, , 75-87.                                                               | 0.4 | 1         |

| 3  | Low-power high-speed CMOS double tail dynamic comparator using self-biased amplification stage and novel latch stage. Analog Integrated Circuits and Signal Processing, 2019, 101, 307-317.                                   | 1.4 | 18        |

| 4  | Design and Performance of High-speed Low-Offset CMOS Double-Tail Dynamic Comparators using Offset Control scheme. , 2019, , .                                                                                                 |     | 3         |

| 5  | Impact of Channel Doping Fluctuation and Metal Gate Work Function Variation in FD-SOI MOSFET for 5nm BOX Thickness. , 2019, , .                                                                                               |     | 4         |

| 6  | Design and Analysis of an Energy-Efficient High-Speed CMOS Double-Tail Dynamic Comparator with Reduced Kickback Noise Effect. Journal of Circuits, Systems and Computers, 2019, 28, 1950157.                                  | 1.5 | 7         |

| 7  | Enhanced Gain Low-Power CMOS Amplifiers: A Novel Design Approach Using Bulk-Driven Load and<br>Introduction to GACOBA Technique. Journal of Circuits, Systems and Computers, 2018, 27, 1850204.                               | 1.5 | 15        |

| 8  | Design of Power Efficient Low-Offset Dynamic Latch Comparator using 90nm CMOS Process. , 2018, , .                                                                                                                            |     | 6         |

| 9  | Optimization for offset and kickback-noise in novel CMOS double-tail dynamic comparator: A<br>low-power, high-speed design approach using bulk-driven load. Microelectronics Journal, 2018, 78, 1-10.                         | 2.0 | 36        |

| 10 | Design of low-power high-speed double-tail dynamic CMOS comparator using novel latch structure. , 2017, , .                                                                                                                   |     | 9         |

| 11 | Enhanced slew rate, constant-g <sub>m</sub> rail-to-rail OpAmp using 1:2 current mirror biasing technique. , 2016. , .                                                                                                        |     | 2         |