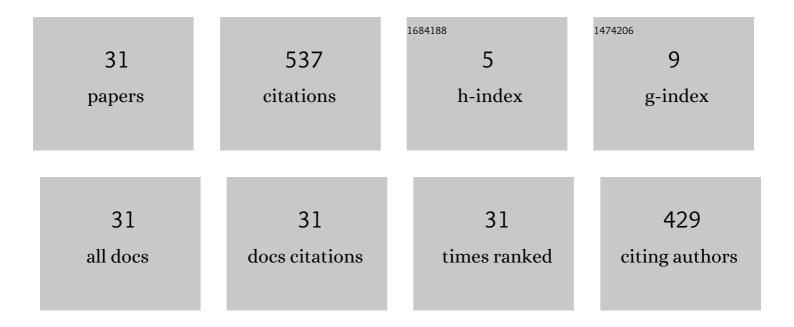

## Ramon Bertran Monfort

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/1579640/publications.pdf Version: 2024-02-01

| #  | Article                                                                                                                                                                     | IF  | CITATIONS |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | Decomposable and responsive power models for multicore processors using performance counters. , 2010, , .                                                                   |     | 107       |

| 2  | Safe limits on voltage reduction efficiency in GPUs. , 2015, , .                                                                                                            |     | 60        |

| 3  | A Systematic Methodology to Generate Decomposable and Responsive Power Models for CMPs. IEEE Transactions on Computers, 2013, 62, 1289-1302.                                | 3.4 | 57        |

| 4  | Voltage Noise in Multi-Core Processors: Empirical Characterization and Optimization Opportunities. , 2014, , .                                                              |     | 52        |

| 5  | Energy accounting for shared virtualized environments under DVFS using PMC-based power models.<br>Future Generation Computer Systems, 2012, 28, 457-468.                    | 7.5 | 35        |

| 6  | Systematic Energy Characterization of CMP/SMT Processor Systems via Automated Micro-Benchmarks. , 2012, , .                                                                 |     | 34        |

| 7  | Accurate energy accounting for shared virtualized environments using PMC-based power modeling techniques. , 2010, , .                                                       |     | 25        |

| 8  | BRAVO: Balanced Reliability-Aware Voltage Optimization. , 2017, , .                                                                                                         |     | 24        |

| 9  | Counter-Based Power Modeling Methods: Top-Down vs. Bottom-Up. Computer Journal, 2013, 56, 198-213.                                                                          | 2.4 | 21        |

| 10 | Droop mitigation using critical-path sensors and an on-chip distributed power supply estimation engine in the z14â,,¢ enterprise processor. , 2018, , .                     |     | 16        |

| 11 | Asymmetric Resilience: Exploiting Task-Level Idempotency for Transient Error Recovery in Accelerator-Based Systems. , 2020, , .                                             |     | 14        |

| 12 | 26.2 Power supply noise in a 22nm z13â,,¢ microprocessor. , 2017, , .                                                                                                       |     | 13        |

| 13 | 2.7 IBM z15: A 12-Core 5.2GHz Microprocessor. , 2020, , .                                                                                                                   |     | 13        |

| 14 | IBM z14: Processor Characterization and Power Management for High-Reliability Mainframe Systems.<br>IEEE Journal of Solid-State Circuits, 2019, 54, 121-132.                | 5.4 | 11        |

| 15 | Local Memory Design Space Exploration for High-Performance Computing. Computer Journal, 2011, 54, 786-799.                                                                  | 2.4 | 10        |

| 16 | Energy Efficiency Boost in the Al-Infused POWER10 Processor. , 2021, , .                                                                                                    |     | 8         |

| 17 | Very Low Voltage (VLV) Design. , 2017, , .                                                                                                                                  |     | 5         |

| 18 | Predictive Guardbanding: Program-Driven Timing Margin Reduction for GPUs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2021, 40, 171-184. | 2.7 | 5         |

| #  | Article                                                                                                                                          | IF  | CITATIONS |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | ChopStiX: Systematic Extraction of Code-Representative Microbenchmarks. , 2018, , .                                                              |     | 4         |

| 20 | Cores, Cache, Content, and Characterization: IBM's Second Generation 14-nm Product, z15. IEEE Journal of Solid-State Circuits, 2021, 56, 98-111. | 5.4 | 4         |

| 21 | Intelligent Adaptation of Hardware Knobs for Improving Performance and Power Consumption. IEEE<br>Transactions on Computers, 2021, 70, 1-16.     | 3.4 | 3         |

| 22 | Al accelerator on IBM Telum processor. , 2022, , .                                                                                               |     | 3         |

| 23 | POTRA. , 2012, , .                                                                                                                               |     | 2         |

| 24 | Characterization of transient error tolerance for a class of mobile embedded applications. , 2014, , .                                           |     | 2         |

| 25 | libPRISM., 2017, , .                                                                                                                             |     | 2         |

| 26 | Asymmetric Resilience for Accelerator-Rich Systems. IEEE Computer Architecture Letters, 2019, 18,<br>83-86.                                      | 1.5 | 2         |

| 27 | MicroGrad: A Centralized Framework for Workload Cloning and Stress Testing. , 2021, , .                                                          |     | 2         |

| 28 | SERMiner : A Framework for Early-stage Reliability Estimation for IBM Processors. , 2021, , .                                                    |     | 2         |

| 29 | Generation of Stressmarks for Early Stage Soft-Error Modeling. , 2019, , .                                                                       |     | 1         |

| 30 | Design space exploration for aggressive core replication schemes in CMPs. , 2011, , .                                                            |     | 0         |

| 31 | POTRA. Performance Evaluation Review, 2012, 40, 427-428.                                                                                         | 0.6 | О         |