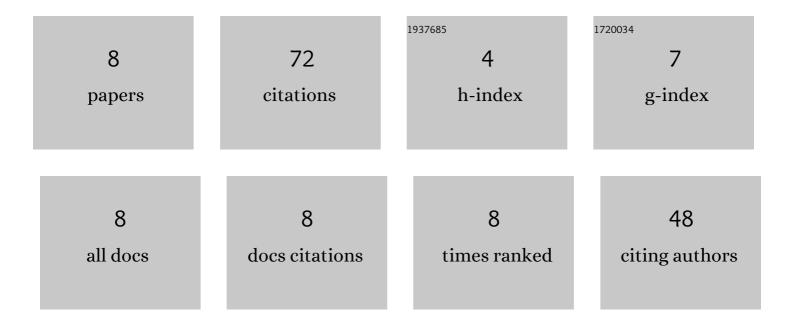

## Arpan Dasgupta

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/1183854/publications.pdf Version: 2024-02-01

ADDAN DASCUDTA

| # | Article                                                                                                                                                                    | IF  | CITATIONS |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1 | Influence of Underlap on Gate Stack DG-MOSFET for analytical study of Analog/RF performance.<br>Superlattices and Microstructures, 2016, 94, 60-73.                        | 3.1 | 33        |

| 2 | Analysis of high-k spacer on symmetric underlap DG-MOSFET with Gate Stack architecture.<br>Superlattices and Microstructures, 2016, 97, 386-396.                           | 3.1 | 12        |

| 3 | Impact of Lateral Straggle on the Analog/RF Performance of Asymmetric Gate Stack Double Gate<br>MOSFET. Superlattices and Microstructures, 2016, 97, 477-488.              | 3.1 | 7         |

| 4 | A linearity based comparison between symmetric and asymmetric lateral diffusion for a 22Ânm<br>Underlapped DG-MOSFET. Superlattices and Microstructures, 2017, 107, 69-82. | 3.1 | 6         |

| 5 | Effect of spacer dielectric engineering on Asymmetric Source Underlapped Double Gate MOSFET using<br>Gate Stack. Superlattices and Microstructures, 2017, 101, 87-95.      | 3.1 | 5         |

| 6 | Impact of Asymmetric Dual-k Spacer in the Underlap Regions of Sub 20Ânm NMOSFET with Gate Stack.<br>Superlattices and Microstructures, 2016, 98, 448-457.                  | 3.1 | 4         |

| 7 | Effect of channel engineering on analog/RF performance of underlapped gatestack DG-MOSFET in Sub-20nm regime. , 2017, , .                                                  |     | 3         |

| 8 | Reliability analysis through linearity and harmonic distortion of a dual-material-gate asymmetric underlapped DGMOSFET. Microelectronics Reliability, 2019, 92, 106-113.   | 1.7 | 2         |