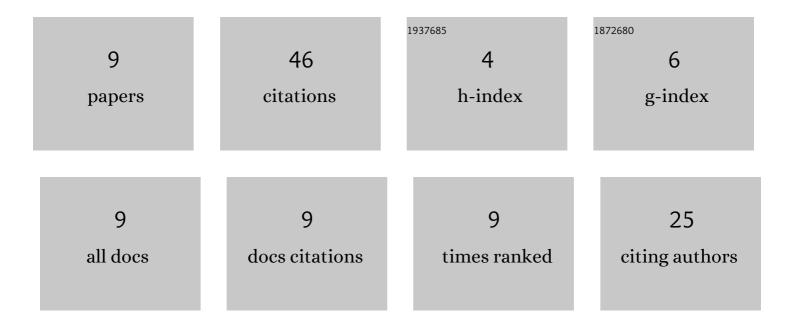

## Sriram S R

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/110965/publications.pdf Version: 2024-02-01

SDIDAM S P

| # | Article                                                                                                                                                                         | IF  | CITATIONS |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1 | A physics-based model for LER-induced threshold voltage variations in double-gate MOSFET. Journal of<br>Computational Electronics, 2020, 19, 622-630.                           | 2.5 | 5         |

| 2 | An Analytical Model of Single-Event Transients in Double-Gate MOSFET for Circuit Simulation. IEEE<br>Transactions on Electron Devices, 2019, 66, 3710-3717.                     | 3.0 | 14        |

| 3 | Analytical Model for RDF-Induced Threshold Voltage Fluctuations in Double-Gate MOSFET. IEEE<br>Transactions on Device and Materials Reliability, 2019, 19, 370-377.             | 2.0 | 3         |

| 4 | A physics-based 3-D potential and threshold voltage model for undoped triple-gate FinFET with interface trapped charges. Journal of Computational Electronics, 2019, 18, 37-45. | 2.5 | 8         |

| 5 | Analytical model of hot carrier degradation in uniaxial strained triple-gate FinFET for circuit simulation. Journal of Computational Electronics, 2018, 17, 163-171.            | 2.5 | 7         |

| 6 | Hot Carrier Reliability in 45 nm Strained Si/relaxed Si <sub>1â^'x</sub> Ge <sub>x</sub> CMOS Based<br>SRAM Cell. , 2018, , .                                                   |     | 1         |

| 7 | Impact of NBTI induced variations on FinFET based Vernier delay line time to digital converter. , 2017, , .                                                                     |     | Ο         |

| 8 | Impact of NBTI induced variations on delay locked loop multi-phase clock generator. Microelectronics<br>Reliability, 2016, 60, 33-40.                                           | 1.7 | 8         |

| 9 | Design of FinFET based frequency synthesizer. , 2015, , .                                                                                                                       |     | 0         |