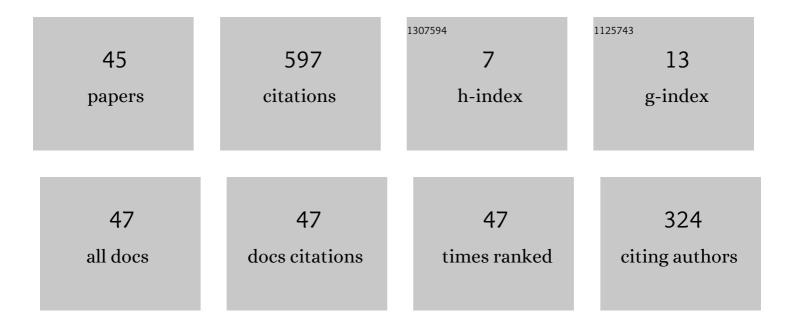

## Eduardo I Boemo

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/10191978/publications.pdf Version: 2024-02-01

Ευμαρίο Ι Βοεμο

8

| #  | Article                                                                                                                                                                                      | IF  | CITATIONS |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | Design of high-speed multiplierless filters using a nonrecursive signed common subexpression algorithm. IEEE Transactions on Circuits and Systems Part 2: Express Briefs, 2002, 49, 196-203. | 2.2 | 152       |

| 2  | Dynamically inserting, operating, and eliminating thermal sensors of FPGA-based systems. IEEE<br>Transactions on Components and Packaging Technologies, 2002, 25, 561-566.                   | 1.3 | 87        |

| 3  | Thermal testing on reconfigurable computers. IEEE Design and Test of Computers, 2000, 17, 84-91.                                                                                             | 1.0 | 54        |

| 4  | Thermal monitoring on FPGAs using ring-oscillators. Lecture Notes in Computer Science, 1997, , 69-78.                                                                                        | 1.3 | 38        |

| 5  | Ring oscillators as thermal sensors in FPGAs: Experiments in low voltage. , 2010, , .                                                                                                        |     | 35        |

| 6  | Clock gating and clock enable for FPGA power reduction. , 2012, , .                                                                                                                          |     | 25        |

| 7  | Low-Power FSMs in FPGA: Encoding Alternatives. Lecture Notes in Computer Science, 2002, , 363-370.                                                                                           | 1.3 | 25        |

| 8  | Some notes on power management on FPGA-based systems. Lecture Notes in Computer Science, 1995, , 149-157.                                                                                    | 1.3 | 20        |

| 9  | Some experiments about wave pipelining on FPGA's. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 1998, 6, 232-237.                                                        | 3.1 | 15        |

| 10 | Rapid Prototyping of a Self-Timed ALU with FPGAs. , 0, , .                                                                                                                                   |     | 14        |

| 11 | A study about FPGA-based digital filters. , 0, , .                                                                                                                                           |     | 11        |

| 12 | Real-time scheduling coprocessor for NIOS II processor. , 2012, , .                                                                                                                          |     | 11        |

| 13 | Fast FPGA-based pipelined digit-serial/parallel multipliers. , 0, , .                                                                                                                        |     | 10        |

| 14 | Statistical power estimation for FPGAs. , 0, , .                                                                                                                                             |     | 10        |

| 15 | Tracking the pipelining-power rule along the FPGA technical literature. , 2013, , .                                                                                                          |     | 10        |

| 16 | Design and FPGA implementation of digit-serial FIR filters. , 0, , .                                                                                                                         |     | 9         |

| 17 | Thermal testing on programmable logic devices. , 0, , .                                                                                                                                      |     | 9         |

|    |                                                                                                                                                                                              |     |           |

18 Power estimations vs. power measurements in Cyclone III devices. , 2011, , .

2

Eduardo I Boemo

0

| #  | Article                                                                                                                                                                             | IF  | CITATIONS |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | FPGA implementation of a binary32 floating point cube root. , 2014, , .                                                                                                             |     | 8         |

| 20 | Efficient fpga-implementation of two's complement digit-serial/parallel multipliers. IEEE Transactions on Circuits and Systems Part 2: Express Briefs, 2003, 50, 317-322.           | 2.2 | 6         |

| 21 | Self-Reconfigurable Constant Multiplier for FPGA. ACM Transactions on Reconfigurable Technology and Systems, 2013, 6, 1-17.                                                         | 2.5 | 6         |

| 22 | Power estimations vs. power measurements in Spartan-6 devices. , 2014, , .                                                                                                          |     | 6         |

| 23 | Proprioception in the ACL-ruptured knee: The contribution of the medial collateral ligament and patellar ligament. An in vivo experimental study in the cat. Knee, 2007, 14, 39-45. | 1.6 | 4         |

| 24 | A Tool for Activity Estimation in FPGAs. Lecture Notes in Computer Science, 2002, , 340-349.                                                                                        | 1.3 | 4         |

| 25 | Watermarking strategies for IP protection of micro-processor cores. , 2010, , .                                                                                                     |     | 3         |

| 26 | A Low Cost System for Self Measurements of Power Consumption in Field Programmable Gate Arrays.<br>Journal of Low Power Electronics, 2017, 13, 1-9.                                 | 0.6 | 3         |

| 27 | FPGA Implementation of a Synchronous and Self-Timed Neuroprocessor. , 0, , .                                                                                                        |     | 2         |

| 28 | Arithmetic Operations and Their Energy Consumption in the Nios II Embedded Processor. , 2008, , .                                                                                   |     | 2         |

| 29 | Real-time phase slopes calculations by correlations using FPGAs. , 2008, , .                                                                                                        |     | 2         |

| 30 | Ro-based PRNG: FPGA implementation and stochastic analysis. , 2014, , .                                                                                                             |     | 2         |

| 31 | Run-Time Reconfiguration to Check Temperature in Custom Computers: An Application of JBits Technology. Lecture Notes in Computer Science, 2002, , 162-170.                          | 1.3 | 2         |

| 32 | Learning VLSI design using programmable logic arrays. , 0, , .                                                                                                                      |     | 1         |

| 33 | Thermal verification on FPGAs. , 2005, , .                                                                                                                                          |     | 1         |

| 34 | Energy Evaluation in the Nios II Processor as a Function of Cache Sizes. , 2008, , .                                                                                                |     | 1         |

| 35 | Protection of microprocessor-based cores for FPL devices. , 2010, , .                                                                                                               |     | 1         |

|    |                                                                                                                                                                                     |     |           |

36 Software security strategies for PC-based education laboratories: A case study. , 0, , .

3

| #  | Article                                                                                                                                     | IF  | CITATIONS |

|----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 37 | Microcontrollers in education: a case-study. , 0, , .                                                                                       |     | 0         |

| 38 | <title>Programmable real-time FIR-filter logic device</title> . , 1995, 2607, 22.                                                           |     | 0         |

| 39 | A-B Nodes Classification for Power Estimation. , 2006, , .                                                                                  |     | 0         |

| 40 | A×B B×A in Terms of Power Consumption: Some Examples on FPGA. , 2007, , .                                                                   |     | 0         |

| 41 | Editorial: Field-programmable logic and applications. IET Computers and Digital Techniques, 2007, 1, 265.                                   | 1.2 | 0         |

| 42 | Viability Study of Soft-Processor Usage for Electronic Collimation Control in Medical Applications. ,<br>2007, , .                          |     | 0         |

| 43 | miniFPGA: An educational app for teaching partitioning, placemnent and routing on Andriod devices. , 2014, , .                              |     | 0         |

| 44 | FPGA structures with concentrated vs distributed memory for images comparison. , 2014, , .                                                  |     | 0         |

| 45 | Evaluation of a Locomotion Algorithm for Worm-Like Robots on FPGA-Embedded Processors. Lecture<br>Notes in Computer Science, 2006, , 24-29. | 1.3 | Ο         |